Время на прочтение

5 мин

Количество просмотров 25K

Введение. Зачем все это?

В этом цикле статей речь пойдет о параллельном программировании.

-

Часть 1. MPI — Введение и первая программа.

-

Часть 2. MPI — Учимся следить за процессами.

-

Часть 3. MPI — Как процессы общаются? Сообщения типа точка-точка.

В бой. Введение

Довольно часто самые сложные алгоритмы требуют огромного количества вычислительных ресурсов в реальных задачах, когда программист пишет код в стандартном его понимании процедурного или Объектно Ориентированного Программирования(ООП), то для особо требовательных алгоритмических задач, которые работают с большим количеством данных и требуют минимизировать время выполнения задачи, необходимо производить оптимизацию.

В основном используют 2 типа оптимизации, либо их смесь: векторизация и распараллеливание

вычислений. Чем же они отличаются?

Вычисления производятся на процессоре, процессор пользуется специальными «хранилищами» данных называемыми регистрами. Регистры процессора напрямую подключены к логическим элементам и требуют гораздо меньшее время для выполнения операций над данными, чем данные из оперативной памяти, а тем более на жестком диске, так как для последних довольно большую часть времени занимает пересылка данных. Так же в процессорах существует область памяти называемая Кэшем, в нем хранятся те значения, которые в данный момент участвуют в вычислениях или будут участвовать в них в ближайшее время, то есть самые важные данные.

Задача оптимизации алгоритма сводится к тому, чтобы правильно выстроить последовательность операций и оптимально разместить данные в Кэше, минимизировав количество возможных пересылок данных из памяти.

Так а чем отличаются векторизация и параллельные вычисления? Векторизация — позволяет выполнять операции над данными целыми векторами. Например для С++: если мы используем AVX инструкции, то у нас есть вектора размером 256 бит, куда мы можем поместить float32 элементы. Получится, что мы можем собрать 2 вектора по (256 / 32) = 8 float32 значений. После чего выполнить над ними одну операцию за такт, хотя если бы мы этого не сделали, то вполне возможно, что аналогичные вычисления прошли бы за 8 операций, а то и больше если брать в учет вычисления индексов конкретных элементов. Однако есть одна проблема: компиляторы нынче довольно умны и довольно хорошо справляются с подобной оптимизацией и сами, поэтому большая часть сил уходит на то чтобы правильно организовать данные.

Параллелизация же позволяет пользоваться не только вычислительными возможностями одного процессора, а множеством процессоров, в том числе и в системах с распределенной памятью, и т.п. В подобных системах как правило намного больше вычислительных мощностей, но этим всем нужно уметь управлять и правильно организовывать параллельную работу на конкретных потоках.

Основная часть

В настоящее время существует много технологий которые позволяют наиболее легко организовать параллельные вычисления, одна из самых популярных на текущий момент это MPI.

MPI — Message Passing Interface (интерфейс передачи сообщений). Название носит смысловой характер, что будет ярко выражено в последующих статьях, а пока все что требуется знать — основной способ взаимодействия параллельных процессов в такой системе — передача сообщений между ними. Это означает что наши потоки будут между собой общаться при обработке данных, а как это уже вопрос реализации.

Существует два основных стиля создания параллельных программ: MIMD(Multiple Instruction Multiple Data — Множественный поток Инструкций, Множественный поток Данных) и SPMD(Single Program Multiple Data — Одна Программа, Множественный поток Данных).

Если сильно упростить, то первая модель берет разные исходные коды программы и выполняет их на разных потоках, а вторая модель берет один исходный код и запускает его на всех выделенных потоках. Программы написанные под стиль MIMD довольно сложно отлаживаются из-за своей архитектуры, поэтому чаще используется модель SPMD. В MPI возможно использовать и то и то, но по стандарту(в зависимости от реализации, разумеется) используется модель SPMD.

Установка

Поскольку MPI — библиотека, то необходимо ее прилинковать к компилятору. В каждой среде это делается по своему и в зависимости от компилятора. Лично я работал на Ubuntu Budgie 20.04 LTS и расскажу инструкцию по установке именно для нее.

В командной строке вводим следующие команды:

[user-name]$ sudo apt-get update

[user-name]$ sudo apt-get install gcc

[user-name]$ sudo apt-get install mpichПервая команда обновляет менеджер пакетов, вторая устанавливает компилятор GCC, если его нет в системе, третья программа устанавливает компилятор через который мы собственно и будем работать с CС++&MPI кодом.

Первые шаги.

MPI-программа — это множество параллельных взаимодействующих процессов, которые работают каждый в своей выделенной области памяти. По сути это N независимых программ, которые общаются между собой в ходе работы. В MPI большинство типов данных уже переопределены и начинаются с аббревиатуры MPI_[Name], далее это будет понятно.

Для понимания того что происходит дальше нужно определиться с несколькими терминами:

Коммуникатор — объект через который общается определенная группа порожденных процессов. В С++/С это тип данных MPI_Comm. Коммуникатор может объединять несколько процессов путем передачи сообщений между ними, при этом коммуникаторов может быть несколько, группы которые они образуют могут как не пересекаться, так пересекаться частично. При старте программы все процессы работают под единым коммуникатором с именем MPI_COMM_WORLD. Кроме него существуют еще коммуникаторы MPI_COMM_SELF, MPI_COMM_NULL, которые содержат только текущий процесс и ни одного процесса соответственно.

Сообщение — набор данных некоторого типа, который передается при коммуникации процессов. Каждое сообщение имеет несколько атрибутов, в частности номер процесса-отправителя, получателя, идентификатор сообщения, коммуникатор и тег.

Тег сообщения — целое не отрицательное число от 0 до 32767(В зависимости от реализации. Максимально возможная величина тега хранится в константе MPI_TAG_UB).

В данном примере не будем использовать пересылку данных, а лишь ознакомимся с основами процедур MPI.ения возможности использования большинства процедур MPI в любой программе должны быть следующие процедуры:

int MPI_Init(int *argc, char ***argv);

int MPI_Finalize(void);Первая процедура предназначения для инициализации параллельной части программы, все другие процедуры, кроме некоторых особых, могут быть вызваны только после вызова процедуры MPI_Init, принимает эта функция аргументы командной строки, через которые система может передавать процессу некоторые параметры запуска. Вторая процедура же предназначена для завершения параллельной части программы.

Для того чтобы проверить работу программы реализуем самую примитивную программку на С++ с применением MPI.

#include <stdio.h>

#include "mpi.h"

int main(int argc, char **argv)

{

printf("Before MPI_INITn");

MPI_Init(&argc, &argv);

printf("Parallel sectn");

MPI_Finalize();

printf("After MPI_FINALIZEn");

return 0;

}Чтобы запустить эту программу сохраним нашу запись в файле с любым названием и расширением *.cpp, после чего выполним следующие действия в консоли (В моем случае код лежит в файле main.cpp):

[user-name]$ mpic++ main.cpp -o main

[user-name]$ mpiexec -n 2 ./main Первая команда скомпилирует нашу MPI-программу, а вторая команда позволяет ее запустить. Заметим, что мы передаем параметры -n 2 во второй строке, зачем это? Таким образом мы сообщаем исполнителю, что нужно запустить 2 параллельных процесса.

Программа просто напечатает несколько строк в зависимости от количества процессов которое вы укажете. Не стоит пугаться если строки «Before …» и «After …» будут отображаться не по одному разу, в зависимости от реализации MPI программа может работать параллельно и вне процедур Init-Finalize.

Итог

В этой краткой статье мы на примере наипростейшей программы научились запускать файлы C++ с MPI кодом и разобрались что за зверь вообще MPI и с чем его едят. В дальнейших туториалах мы рассмотрим уже более полезные программы и наконец перейдем ко коммуникации между процессами.

Текущая версия страницы пока не проверялась опытными участниками и может значительно отличаться от версии, проверенной 3 февраля 2022 года; проверки требует 1 правка.

| Одиночный поток команд (single instruction) |

Множество потоков команд (multiple instruction) |

|

|---|---|---|

| Одиночный поток данных (single data) |

SISD (ОКОД) |

MISD (МКОД) |

| Множество потоков данных (multiple data) |

SIMD (ОКМД) |

MIMD (МКМД) |

MIMD (англ. Multiple Instruction stream, Multiple Data stream — Множественный поток Команд, Множественный поток Данных, сокращённо МКМД) — концепция архитектуры компьютера, используемая для достижения параллелизма вычислений. Один из классов вычислительных систем в классификации Флинна.

Машины имеют несколько процессоров, которые функционируют асинхронно и независимо. В любой момент различные процессоры могут выполнять различные команды над различными частями данных. MIMD-архитектуры могут быть использованы в целом ряде областей, таких, как системы автоматизированного проектирования / автоматизированное производство, моделирование, а также коммуникатор связей (англ. communication switches). MIMD-машины могут быть либо с общей памятью, либо с распределяемой памятью. Эта классификация основана на том, как MIMD-процессоры получают доступ к памяти. Этот класс предполагает, что в вычислительной системе есть несколько устройств обработки команд, объединённых в единый комплекс и работающих каждое со своим потоком команд и данных.

Обработка разделена на несколько потоков, каждый с собственным аппаратным состоянием процессора, в рамках единственного определённого программным обеспечением процесса или в пределах множественных процессов. Поскольку система имеет несколько потоков, ожидающих выполнения (системные или пользовательские потоки), эта архитектура эффективно использует аппаратные ресурсы.

В MIMD могут возникнуть проблемы взаимной блокировки и состязания за обладание ресурсами, так как потоки, пытаясь получить доступ к ресурсам, могут столкнуться непредсказуемым способом. MIMD требует специального кодирования в операционной системе компьютера, но не требует изменений в прикладных программах, кроме случаев, когда программы сами используют множественные потоки (MIMD прозрачен для однопоточных программ под управлением большинства операционных систем, если программы сами не отказываются от управления со стороны ОС). И системное, и пользовательское программное обеспечение, возможно, должны использовать программные конструкции, такие, как семафоры, чтобы препятствовать тому, чтобы один поток вмешался в другой, в случае если они содержат ссылку на одни и те же данные. Такое действие увеличивает сложность кода, снижает производительность и значительно увеличивают количество необходимого тестирования, хотя обычно не настолько, чтобы свести на нет преимущества многопроцессорной обработки.

Подобные конфликты могут возникнуть на аппаратном уровне между процессорами, и должны обычно решаться аппаратными средствами, или комбинацией программного обеспечения и оборудования.

Принципы построения компьютера

Основным принципом построения всех современных компьютеров является программное управление. В его основе лежит представление алгоритма решения любой задачи в виде программы вычислений.

Все вычисления, предписанные алгоритмом решения задачи, должны быть представлены в виде программы, состоящей из последовательности управляющих слов _ команд. Каждая команда содержит указания на конкретную выполняемую операцию, места нахождения (адреса) операндов и ряд служебных признаков. Операнды _ переменные, значения которых участвуют в операциях преобразования данных. Программы и обрабатываемые ими данные должны совместно храниться в памяти компьютера.

Для доступа к программам, командам и операндам используются их адреса. В качестве адресов выступают номера ячеек памяти компьютера, предназначенных для хранения объектов. Информация (командная и данные: числовая, текстовая, графическая и другая информация) кодируется двоичным кодом (цифрами 0 и 1). Поэтому различные типы информации, размещенные в памяти, практически неразличимы, идентификация их возможна лишь при выполнении программы, согласно ее логике, по контексту.

Выполнение каждой команды программы предполагает многократное обращение к памяти (выборка команд, выборка операндов, отсылка результатов и т.п.). В первых структурах ЭВМ использовалось централизованное управление, при котором одна и та же аппаратура выполняла и основные, и вспомогательные действия. Это было оправдано для первых дорогих машин, но не позволяло выполнять параллельные работы. Эволюция вычислительной техники потребовала децентрализации.

Децентрализация построения и управления вызвала к жизни такие элементы, которые являются общим стандартом структур современных компьютеров:

- модульность построения;

- магистральность;

- иерархия управления.

Модульность построения предполагает выделение в структуре компьютера автономных, функционально, логически и конструктивно законченных устройств: процессор, модуль памяти, накопитель на магнитном диске, дисплей и т.п.

Модульная конструкция компьютера делает его открытой системой, способной к адаптации и совершенствованию. К нему можно подключать дополнительные устройства, улучшая его технические и экономические показатели. Появляется возможность наращивания вычислительной мощи, улучшения структуры путем замены отдельных устройств на более совершенные, изменения и управления конфигурацией системы, приспособления ее к конкретным условиям применения в соответствии с требованиями пользователей.

В качестве основных средств подключения и объединения модулей в систему используются магистрали, или шины. Стандартная система сопряжения (интерфейс) обеспечивает возможность формирования требуемой конфигурации, гибкость структуры и адаптацию к изменяющимся условиям функционирования.

В современных вычислителях принцип децентрализации и параллельной работы распространен как на периферийные устройства, так и на сами компьютеры, их процессоры. Появились вычислительные системы, которые содержат несколько вычислителей, работающих согласованно и параллельно. Внутри самого компьютера произошло еще более резкое разделение функций между средствами обработки. Появились отдельные специализированные процессоры, например, сопроцессоры, выполняющие обработку чисел с плавающей точкой, матричные процессоры и др.

Модульность структуры потребовала стандартизации и унификации оборудования, номенклатуры технических и программных средств, средств сопряжения — интерфейсов, конструктивных решений, унификации типовых элементов замены, элементной базы и нормативно-технической документации. Все это способствовало улучшению технических и эксплуатационных характеристик компьютеров, росту технологичности их производства.

Децентрализация управления предполагает иерархическую организацию структуры компьютера. Главный или центральный модуль системы определяет последовательность работ подчиненных модулей и их инициализацию, после чего они продолжают работу по собственным программам управления. Результаты выполнения требуемых операций представляются ими «вверх по иерархии» для правильной координации всех работ. Подключаемые модули могут, в свою очередь, использовать специальные шины, или магистрали, для обмена управляющими сигналами, адресами и данными.

Иерархический принцип построения и управления характерен не только для структуры компьютера в целом, но и для отдельных его подсистем. Например, по этому же принципу строится система памяти.

Децентрализация управления и структуры компьютера позволила перейти к более сложным многопрограммным (мультипрограммным) режимам. При этом в компьютере одновременно могут обрабатываться несколько программ пользователей.

Структурные схемы и взаимодействие устройств компьютера

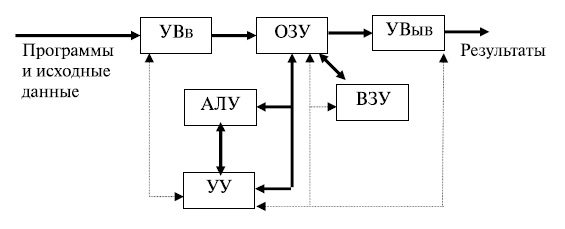

Классическая схема компьютера, отвечающая программному принципу управления, логично вытекает из последовательного характера преобразований, выполняемых человеком по некоторому алгоритму (программе). Обобщенная структурная схема ЭВМ первых поколений представлена на рис.13.2.

В любом компьютере имеются устройства ввода информации (УВв), с помощью которых пользователи вводят программы решаемых задач и данные. Введенная информация сначала полностью или частично запоминается в оперативном запоминающем устройстве (ОЗУ), а затем переносится во внешнее запоминающее устройство (ВЗУ), предназначенное для длительного хранения информации, где преобразуется в специальный информационный объект — файл.

Рис.

13.2.

Структурная схема первых компьютеров

При использовании файла в вычислительном процессе его содержимое переносится в ОЗУ. Затем программная информация команда за командой считывается в устройство управления.

Устройство управления (УУ) предназначается для автоматического выполнения программ путем принудительной координации всех остальных устройств. Цепи сигналов управления показаны на рис.13.2 штриховыми линиями. Вызываемые из ОЗУ команды дешифрируются устройством управления: определяют код операции, которую необходимо выполнить следующей, и адреса операндов, принимающих участие в данной операции.

Арифметико-логическое устройство (АЛУ) выполняет арифметические и логические операции над данными. Основной частью АЛУ является операционный автомат, в состав которого входят сумматоры, счетчики, регистры, логические преобразователи и др. Он каждый раз перестраивается на выполнение очередной операции. Результаты выполнения отдельных операций сохраняются для последующего использования на одном из регистров АЛУ или записываются в память. Отдельные признаки результатов r ( и др.) устройство управления использует для изменения порядка выполнения команд программы. Результаты, полученные после выполнения всей программы вычислений, передаются на устройство вывода информации (УВыв). В качестве УВыв могут использоваться экран дисплея, принтер, графопостроитель и др.

и др.) устройство управления использует для изменения порядка выполнения команд программы. Результаты, полученные после выполнения всей программы вычислений, передаются на устройство вывода информации (УВыв). В качестве УВыв могут использоваться экран дисплея, принтер, графопостроитель и др.

Классическая структура компьютера представляла собой «удивительно изящное инженерное решение», хорошо отвечающее тогдашнему уровню развития промышленных технологий. Она стала фактическим стандартом (de facto), которому стали следовать производители вычислительной техники.

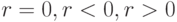

В персональных компьютерах, относящихся к компьютерам четвертого поколения, произошло дальнейшее изменение структуры (рис.13.3). Соединение всех устройств в единую машину обеспечивается с помощью общей шины, представляющей собой линии передачи данных, адресов, сигналов управления и питания. Единая система аппаратурных соединений значительно упростила структуру, сделав ее децентрализованной. Все передачи данных по шине осуществляются под управлением сервисных программ.

Рис.

13.3.

Структура ПК

Ядро ПК образуют процессор, основная память (ОП), состоящая из оперативной памяти и постоянного запоминающего устройства (ПЗУ), и видеопамять. ПЗУ предназначается для записи и постоянного хранения наиболее часто используемых программ управления.

Подключение всех внешних устройств (ВнУ), дисплея, клавиатуры, внешних ЗУ и др. обеспечивается через соответствующие адаптеры — согласователи скоростей работы сопрягаемых устройств, или контроллеры — специальные устройства управления периферийной аппаратурой. Контроллеры в ПК играют роль каналов ввода-вывода. В качестве особых устройств следует выделить таймер — устройство измерения времени, и контроллер прямого доступа к памяти (КПД) — устройство, обеспечивающее доступ к ОП, минуя процессор.

Организацию согласованной работы шин и устройств выполняют микросхемы системной логики, называемые чипсетом (Chipset). Большинство наборов микросхем системной логики имеют ярко выраженную иерархическую структуру построения, отвечающую уровням высокоскоростных и ввода-вывода данных. Уровень высокоскоростных устройств образуют процессоры, видеопамять, оперативная память; уровень низко-скоростных устройств образуют любые внешние устройства.

Компьютерные системы

Полувековая история развития вычислительной техники была связана с совершенствованием классической структуры компьютера, имеющей следующие отличительные признаки:

- ядро компьютера — процессор — единственный вычислитель в структуре, дополненный каналами обмена информацией и памятью;

- линейная организация ячеек всех видов памяти фиксированного размера;

- одноуровневая адресация ячеек памяти, стирающая различия между всеми типами информации;

- внутренний машинный язык низкого уровня, при котором команды содержат элементарные операции преобразования простых операндов;

- последовательное централизованное управление вычислениями;

- достаточно примитивные возможности устройства ввода-вывода.

Классическая структура компьютера уже сослужила добрую службу человечеству. В ходе эволюции она была дополнена целым рядом частных доработок, позволяющих ликвидировать наиболее «узкие места» и обеспечить максимальную производительность в рамках достигнутых технологий. Однако, несмотря на все успехи, классическая структура уже не обеспечивает возможностей дальнейшего наращивания производительности. Теория и практика построения компьютеров подошли к рубежам микроэлектроники, за которыми стоят множество практически неразре-шимых проблем в областях системотехники, дальнейшего наращивания частоты работы микросхем, программирования, компиляции и т.д.

Дальнейшее поступательное развитие вычислительной техники напрямую связано с переходом к параллельным вычислениям, с идеями построения многопроцессорных систем и сетей, объединяющих большое количество отдельных процессоров и (или) ЭВМ. Здесь появляются огромные возможности совершенствования средств вычислительной техники. Но следует отметить, что при несомненных практических достижениях в области параллельных вычислений до настоящего времени отсутствует их единая теоретическая база.

С появлением в начале нового тысячелетия многоядерных микропроцессоров эра компьютеров классической структуры и связанных с ними последовательных вычислений заканчивается. На смену идут новые параллельные структуры с новыми принципами их построения. Они становятся экономически более выгодными. Будущее вычислительной техники — именно за этими системами.

Под вычислительной (компьютерной) системой (ВС) понимают совокупность взаимосвязанных и взаимодействующих процессоров или ЭВМ, периферийного оборудования и программного обеспечения, предназначенную для сбора, хранения, обработки и распределения информации. Отличительной особенностью ВС по отношению к ЭВМ является наличие в них нескольких вычислителей, реализующих параллельную обработку. Создание ВС преследует следующие основные цели: повышение производительности системы за счет ускорения процессов обработки данных, повышение надежности и достоверности вычислений, предоставление пользователям дополнительных сервисных услуг и т.д.

Основные принципы построения, закладываемые при создании ВС:

- возможность работы в разных режимах;

- модульность структуры технических и программных средств, которая позволяет совершенствовать и модернизировать вычислительные системы без коренных их переделок;

- унификация и стандартизация технических и программных решений;

- иерархия в организации управления процессами;

- способность систем к адаптации, самонастройке и самоорганизации;

- обеспечение необходимым сервисом пользователей при выполнении вычислений.

Существует большое количество признаков, по которым классифицируют вычислительные системы: по целевому назначению и выполняемым функциям, по типам и числу ЭВМ или процессоров, по архитектуре системы, режимам работы, методам управления элементами системы, степени разобщенности элементов вычислительной системы и др. Однако основными из них являются признаки структурной и функциональной организации вычислительной системы.

Большое разнообразие структур ВС затрудняет их изучение. Поэтому их классифицируют с учетом их обобщенных характеристик. С этой целью вводится понятие «архитектура системы».

Архитектура ВС — совокупность характеристик и параметров, определяющих функционально-логическую и структурную организацию системы и затрагивающих в основном уровень параллельно работающих вычислителей. Понятие архитектуры охватывает общие принципы построения и функционирования, наиболее существенные для пользователей, которых больше интересуют возможности систем, а не детали их технического исполнения. Поскольку ВС появились как системы параллельной обработки, рассмотрим классификацию архитектур именно c этой точки зрения.

Классификация архитектур была предложена М. Флинном (M. Flynn) в начале 60-хгг. В ее основу заложено два возможных вида параллелизма: независимость потоков заданий (команд), существующих в системе, и независимость (несвязанность) данных, обрабатываемых в каждом потоке. Классификация до настоящего времени еще не потеряла своего значения. Однако подчеркнем, что, как и любая классификация, она носит временный и условный характер. Своим долголетием она обязана тому, что оказалась справедливой для ВС, в которых вычислительные модули построены на принципах классической структуры ЭВМ. С появлением систем, ориентированных на потоки данных и использование ассоциативной обработки, эта классификация может быть некорректной.

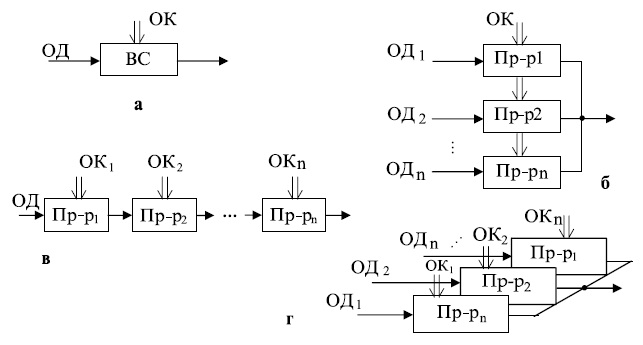

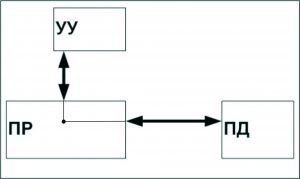

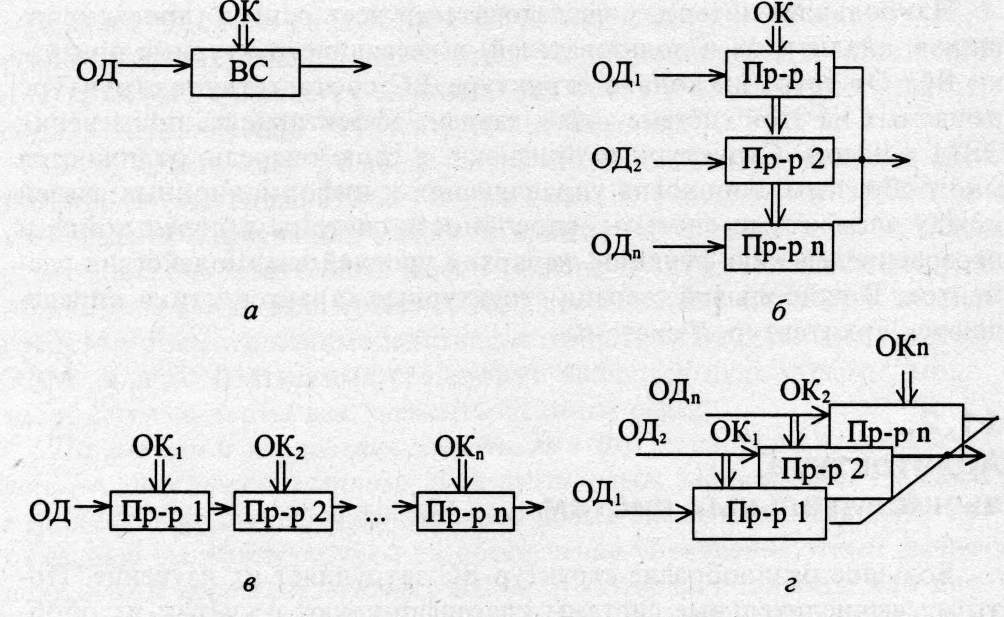

Согласно данной классификации существует четыре основных архитектуры ВС, представленных на рис.13.4:

- одиночный поток команд — одиночный поток данных (ОКОД), в английском варианте Single Instruction Single Data (SISD) — одиночный поток инструкций — одиночный поток данных (рис.13.4a);

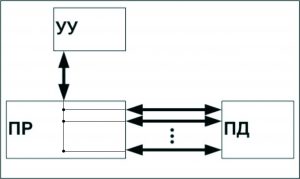

- одиночный поток команд — множественный поток данных (ОКМД), или Single Instruction Multiple Data (SIMD) — одиночный поток инструкций — одиночный поток данных (рис.13.4б);

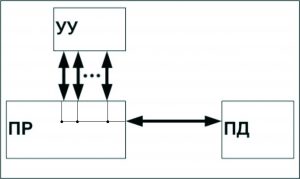

- множественный поток команд — одиночный поток данных (МКОД), или Multiple Instruction Single Data (MISD) — множественный поток инструкций — одиночный поток данных (рис.13.4в);

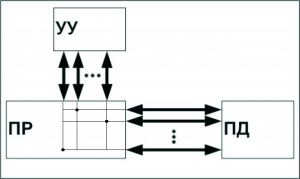

- множественный поток команд — множественный поток данных (МКМД), или Multiple Instruction Multiple Data (MIMD) — множественный поток инструкций — множественный поток данных (рис.13.4г).

Коротко рассмотрим отличительные особенности каждой из архитектур.

Архитектура ОКОД охватывает все однопроцессорные и одномашинные варианты систем, то есть варианты с одним вычислителем. Все ЭВМ классической структуры попадают в этот класс. Здесь параллелизм вычислений обеспечивается путем совмещения выполнения операций отдельными блоками АЛУ, а также параллельной работой устройств ввода-вывода информации и процессора. Закономерности организации вы-числительного процесса в этих структурах достаточно хорошо изучены.

Архитектура ОКМД предполагает создание структур векторной или матричной обработки. Системы этого типа обычно строятся как однородные, т.е. процессорные элементы, входящие в систему, идентичны и все они управляются одной и той же последовательностью команд. Однако каждый процессор обрабатывает свой поток данных. Под эту схему хорошо подходят задачи обработки матриц или векторов (массивов), задачи решения систем линейных и нелинейных, алгебраических и дифференциальных уравнений, задачи теории поля и др. В структурах данной архитектуры желательно обеспечивать соединения между процессорами, соответствующие реализуемым математическим зависимостям. Как правило, эти связи напоминают матрицу, в которой каждый процессорный элемент связан с соседними.

Рис.

13.4.

Архитектуры вычислительных систем: а) ОКОД (SISD) — архитектура; б) ОКМД (SIMD) — архитектура; в) МКОД (MISD) — архитектура; г) МКМД (MIMD) — архитектура

Эту схему использовали и используют все суперЭВМ без исключения, начиная с таких известных систем, как Cyber-205 и Gray различных модификаций. Узким местом подобных систем является необходимость изменения коммутации между процессорами, когда связь между ними отличается от матричной. Кроме того, задачи, допускающие широкий матричный параллелизм, составляют достаточно узкий класс задач. Структуры ВС этого типа по существу являются структурами специализированных суперЭВМ.

Архитектура МКОД предполагает построение своеобразного процессорного конвейера, в котором результаты обработки передаются от одного процессора к другому по цепочке. Выгоды такого вида обработки понятны. Прототипом таких вычислений может служить схема любого производственного конвейера. В современных ЭВМ по этому принципу реализована схема совмещения операций, в которой различные функциональные блоки работают параллельно, и каждый из них делает свою часть в общем цикле обработки команды.

В ВС этого типа конвейер должны образовывать группы процессоров. Однако при переходе на системный уровень очень трудно выявить подобный регулярный характер в универсальных вычислениях. Кроме того, на практике нельзя обеспечить и «большую длину» такого конвейера, при которой достигается наивысший эффект. Вместе с тем конвейерная схема нашла применение в так называемых скалярных процессорах суперЭВМ — они применяются как специальные процессоры для поддержки векторной обработки.

Архитектура МКМД предполагает, что все процессоры системы работают с различными программами и с индивидуальным набором данных. В простейшем случае они могут быть автономны и независимы. Такая схема использования ВС часто применяется во многих крупных вычислительных центрах для увеличения пропускной способности центра.

Наибольший интерес представляет организация согласованной работы процессоров системы, когда каждый элемент делает часть общей программы. Общая теоретическая база такого вида работ пока только создается. Но можно привести примеры большой эффективности этой модели вычислений. Подобные системы могут быть многомашинными и многопроцессорными. Переход на многоядерные микропроцессоры позволяет создавать мощные центры параллельной обработки, имеющие в своем составе тысячи процессоров. Проектировщики компьютерных систем сосредотачивают свои усилия на разработках разноплановых структур ВС (сосредоточенных и распределенных систем) именно в архитектуре МКМД.

Контрольные вопросы

- Каково содержание понятия «структура компьютера»?

- По каким техническим характеристикам осуществляется оценка и выбор компьютера?

- Что представляет собой класс карманных персональных компьютеров?

- Каковы основные тенденции развития компьютеров?

- Объясните суть принципа иерархии построения ЭВМ.

- Перечислите отличительные особенности классической структуры ЭВМ.

- Каковы отличительные особенности структуры ПК?

- Объясните многообразие шин, используемых в структуре ПК.

- Каковы основные предпосылки появления и развития компьютерных систем?

- Какие принципы положены в основу классификации архитектур компьютерных систем?

Классификация архитектур вычислительных систем по Флинну. Какие существуют типы параллелизма? Организация памяти при параллельной обработки данных.

Классификация архитектур вычислительных систем по Флинну

Как известно, из классификаций архитектур вычислительных систем самой первой и наиболее известной является представленная в 1966 [1] году М.Флинном. Данная классификация основывается на понятии потока – последовательность команд, элементов или данных, обрабатываемая процессором. Флинн выделяет четыре класса архитектур на основе числа потоков команд и потоков данных: SISD,MISD,SIMD,MIMD.

SISD (single instruction stream / single data stream) – одиночный поток команд и одиночный поток данных. К данному классу принадлежат классические последовательные машины, или их ещё называют, машины фон-неймановского типа. Данные машины имеют только один поток команд, обрабатывающиеся последовательно друг за другом и каждая команда инициирует одну операцию с одним потоком данных. Все однопоточные программы используют вычислительную систему в этом режиме.

SIMD (single instruction stream / multiple data stream) – одиночный поток команд и множественный поток данных. Подобного рода архитектуры сохраняют один поток команд, включающий, векторные команды, в отличие от предыдущего класса. Это позволяет выполнять одну арифметическую операцию сразу над многими данными – элементами вектора. Примерами SIMD-машин являются системы CPP DAP, Gamma II и Quadrics Apemille. Другим подклассом SIMD-систем являются векторные компьютеры.

MISD (multiple instruction stream / single data stream) – множественный поток команд и одиночный поток данных. Данный класс предполагает, что в архитектуре имеется множество процессоров, которые обрабатывают один и тот же поток данных. Однако до сих пор нет реального примера существования вычислительной системы, построенной на данном принципе. Как аналог работы такой системы, можно представить работу банка. С любого терминала можно подать команду и что-то сделать с имеющимся банком данных. Так как база данных одна, а команд много, то это и будет множественный поток команд и одиночный поток данных.

MIMD (multiple instruction stream / multiple data stream) – множественный поток команд и множественный поток данных. В данном классе, обрабатывается несколько данных, для которых выполняется несколько команд. К данному классу можно отнести многоядерные системы, а также все суперскалярные процессоры в общем виде.

В книге К.Ванга и Ф.Бриггса [2] сделаны некоторые дополнения к классификации Флина. Оставляя четыре ранее введенных базовых класса (SISD, SIMD, MISD, MIMD), авторы внесли следующие изменения.

Класс SISD разбивается на два подкласса:

- архитектуры с единственным функциональным устройством, например, PDP-11;

- архитектуры, имеющие в своем составе несколько функциональных устройств — CDC 6600, CRAY-1, FPS AP-120B, CDC Cyber 205, FACOM VP-200.

В класс SIMD также вводится два подкласса:

- архитектуры с пословно-последовательной обработкой информации — ILLIAC IV, PEPE, BSP;

- архитектуры с разрядно-последовательной обработкой — STARAN, ICL DAP.

В классе MIMD авторы различают:

- вычислительные системы со слабой связью между процессорами, к которым они относят все системы с распределенной памятью, например, Cosmic Cube,

- и вычислительные системы с сильной связью (системы с общей памятью), куда попадают такие компьютеры, как C.mmp, BBN Butterfly, CRAY Y-MP, Denelcor HEP.

Типы параллелизма

В источнике [3] выделяют четыре типа параллелизма: параллелизм на уровне битов, команд, данных, а также задач.

Параллелизм на уровне битов

При реализации операций обеспечивается максимальное распараллеливание, так, например, при осуществление сложения битов числа все биты машинного слова одновременно складываются, а так же используются специальный механизм учета переносов [4]. Чтобы увеличить диапазон чисел, обрабатываемых одной командой, следует увеличить размер машинного слова. Так, выполнен переход от 8-ми до 16-ти и далее к 32 разрядному машинному слову. На данный момент процессоры имеют 64-разрядное машинное слово, некоторые команды могут работать с 128-разрядными данными (процессор Larrabee работает с данными размером 512 битов). При использование машинного слова с большей разрядностью быстрее обрабатываются большие числа. Чтобы обработать 32-битное число для 16-битной машины требуется как минимум 2 команды, а для 32-битной – только одна. Но это верно не для всех 64-битных процессоров, ведь в них реализованы не все операции над 64-битными числами. так же ограничено использование команд, которые в результате дают 128-битные числа и числа большей разрядности.

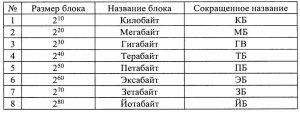

Для определения диапазона адресного пространства также используется машинное слово. Вычислительная система работает с диапазоном адресного пространства, так как оно используется для задания адреса. Для 32-битных вычислительных систем максимальный адрес -1, адресное пространство составляет 4 ГБ. Для 64-битного машинного слова адресное пространство составляет или 16 ГБ. В табл. 1 представлены названия единиц измерения памяти.

таблица 1

У первых вычислительных систем все числа занимали как минимум одно машинное слово, это приводило к неэффективному распределению памяти при задании небольших чисел. Для обеспечения эффективного распределения памяти в нынешних вычислительных системах, следует использовать данные разной длинны. Необходимость увеличения адресного пространства также является следствием усложнения решаемых задач. Для того, чтобы эффективно использовать 64-битные процессоры следует использовать операционную систему для работы с процессорами в 64-х битном режиме, а не использовать возможности этих процессоров работать в 32-битном режиме. Система Linux была первой операционной системой, которая полностью поддерживала работу процессора в этом режиме, далее появилась версия Microsoft Windows XP и Vista. На сегодняшний момент уже используются системы с оперативной памятью 16 ГБ, серверы с оперативной памятью 256ГБ, 8ГБ модули с оперативной памятью в серийном производстве.

Далее следует рассмотреть собственно параллелизм. Его можно реализовать как с помощью конвейера, так и суперескалярности, т.е. наличия нескольких независимых блоков для выполнения команд.

Параллелизм на уровне команд. Конвейер

Давно уже известна идея использования конвейера для увеличения производительности выполнения сложных операций. Происходит деление команды на независимые микрокоманды, время выполнения которых примерно одинаково. Количество микрокоманд равно числу блоков конвейера. Блоки конвейера последовательно обрабатывают очередную команду, выполняя ее микрокоманды. Полностью выполненной команда считается только после завершения обработки последним блоком конвейера.

Конвейерный принцип выполнения команд впервые был использован в машине ATLAS, 1962 г. [5], разработанной в Манчестерском университете. Выделяют 4 стадии выполнения команд: выборка команды, вычисление адреса операнда, выборка операнда и выполнение операции. Для Pentium в конвейер добавлен еще один блок записи результата. С помощью конвейеризации получилось уменьшить время выполнения команд с 6 до 1,6 микросекунд.

Время выполнения одной команды при ее последовательном выполнении от начала до конца примем за 1. Если конвейер состоит из m устройств (ступеней), то длина конвейер равна m. Если не брать в расчет накладные расходы, связанные с «перемещением» результатов выполнения предыдущих операций, то чтобы выполнить одну микрооперацию потребуется 1/m единиц времени. Далее выясним время выполнения программы, которая состоит из n последовательных команд без конвейера и с конвейером. Без конвейера потребуется n единиц времени (при том что время выполнения одной команды принято за 1).

Если использовать конвейер, то первая команда будет выполняться 1 единицу, а каждая очередная команда будет заканчиваться с интервалом 1/m единиц времени. Общее время выполнения такой программы равно 1+(n–1)/m.

Сравним полученные значения для n=100 команд и m=5 блоков конвейера. Без конвейера потребуется T1=100 (единиц времени), с конвейером T2=1+99/5=21 (единиц времени), т.е. почти в 5 раз быстрее. Конвейер позволяет увеличить производительность процессора, что интересно коэффициент ускорения почти прямо пропорционален длине конвейера. Именно поэтому длина конвейера для современных процессоров значительно больше 5. Конвейер Pentium 4 состоит из 35 блоков. Фактически увеличение числа блоков конвейера эквивалентно увеличению тактовой частоты, так как приводит к уменьшению времени выполнения одной команды.

Возникает тогда такой вопрос: можно ли бесконечно увеличивать число блоков конвейера? Нет, так как увеличение числа блоков способствует усложнению архитектуры процессора, увеличивает его тепловыделение. Время выполнения микрокоманды становится соизмеримым с накладными расходами, это уменьшает эффективность использования конвейера. Незнание свойств конвейера может поспособствовать потери производительности. Доказательством этого можно представить данный пример. Пусть в программе используется команда перехода. Для конвейера длиной 5 блоков адрес перехода определяется блоком 3, команду выполняет блок № 4 т.е. блоки второй половины конвейера. К моменту выполнения команды очередные 3 команды уже будут обработаны, несмотря на необходимость обрабатывать совсем другие команды. Такую ситуацию называют остановом конвейера. После того как определились адреса перехода, результаты обработки очередных команд должны быть аннулированы, а следующая команда, находящаяся по адресу перехода, начинает выполняться сначала. Если увеличить длину конвейера соответственно произойдет увеличение потерь, связанных с использованием команд перехода. Современные процессоры имеют блоки прогнозирования переходов, которые уменьшают потери, связанные с наличием команд перехода. Знание алгоритмов предсказания позволит снизить потери, связанные с командами перехода. Далее будут рассмотрены некоторые из них.

Команды сериализации

Конвейер считается одним из способов параллельного выполнения команды. Команды процессора имеют особые команды, которые чтобы начать выполнение ждут завершения всех начатых команд. При их выполнении другие команды не выполняются, данные команды имеют название команды сериализации. Приведем пример команды сериализации – команда cupid, использующаяся для определения особенностей процессора. Чтобы увеличить точность измерения времени, данную команду следует использовать перед началом и в конце замеров.

Предсказание переходов

Имеет свое начало с процессора типа Pentium. Дает возможность уменьшить потери производительности конвейера из-за наличия переходов.

Существует статистическое и динамическое предсказание. Для команд перехода, выполняющиеся в первый раз, используется статистическое предсказание. Для процессора типа Pentium – должна выполняться следующая команда, т.е. фактически нет предсказания.

Для процессоров имеющих более совершенный вид считалось, что ссылка вперед – перехода не будет, а ссылка назад – что переход будет. Это потому что, ссылка назад соответствует циклу, а пишутся циклы чтобы многократно выполнять один и тот же участок кода. Поэтому, статистическое предсказание верно, когда оператор условного перехода при первом его выполнении перехода не существует, т.е. имеет место естественный порядок выполнения команд. Исключением являются только циклы.

В процесс статистического предсказания команда заноситься в буфер предсказания перехода вместе с адресом, куда фактически выполняется переход. Так же устанавливается флаг в 1, если переход был.

Динамическое предсказание для Pentium. Данное предсказание применяется для команд перехода, выполняющихся повторно и которые уже имеют информацию. Каждая команда перехода имеет свой адрес (Адрес1), адрес, куда необходимо перейти (Адрес2) и битовые флаги (два флага). Если хотя бы один флаг из двух установлен в 1, то прогнозируется наличие перехода. Прогнозируется отсутствие перехода, при обоих флагах равны 0.

В дальнейшем в зависимости от того имеется переход или нет, значения флагов корректируются. Если переход есть и есть флаг, равный 0, то он устанавливается в 1. Если перехода нет и есть флаг равный 1, то он сбрасывается в 0. Данный алгоритм способствует минимизации числа ошибок, если очень маленькая вероятность наличия или отсутствия переходов. Если наличие переходов и их отсутствие равновероятны, то вероятность ошибок максимальна.

Динамическое предсказание для Pentium 2 и выше. Данное предсказание применяется для команд перехода, выполняющихся повторно и которые уже имеют информацию. Каждая команда перехода имеет свой адрес (Адрес1), адрес, куда необходимо перейти (Адрес2), битовые флаги (4 флага) и счетчик исполнения команды по модулю 4, наращивающийся при каждом выполнении команды. Когда происходит первое выполнение, команды перехода записываются в свободную строку буфера (все поля нулевые) Адрес1, Адрес2 и один флаг, номер которого соответствует счетчику исполнения команд, устанавливается в 1, если переход был. Далее, если соответствующий флаг равен 1, то имеется наличие перехода, если флаг равен 0, то отсутствие перехода. При варианте, что предсказание о переходе оказалось ошибочным, соответствующий флаг инвертируется. Данный алгоритм сокращает количество ошибок при периодическом характере наличия и отсутствия ошибок. К ошибкам приводят все нарушения периода, в том числе и при вычислении периода.

Рассмотренные выше алгоритмы предсказания все время усовершенствуются для минимизации потерь, но свести на данный момент их к нулю не могут. По этой причине рекомендуется уменьшать число команд перехода в программе, причем чем мощнее, а следовательно, с более длинным конвейером используется процессор, тем более требуется.

Параллелизм на уровне команд. Суперскалярность

Все команды программы делятся на независимые и зависимые команды.

Команды называются зависимыми, если их операнды определяются предшествующими командами. Независимыми командами называют те, которые используют константы, введенные данные или данные, для которых команды уже гарантированно выполнены. Команды, готовые для выполнения – это независимые команды. Их можно выполнять одновременно, если имеются свободные устройства для выполнения этих команд.

Суперскалярные процессоры используются для истинного распараллеливания вычислений. Которые имеют не одно, а несколько однотипных устройств для выполнения операций.

CDC 6600 (1964) [5] был первым компьютером, который имел несколько функциональных блоков. Данный компьютер выпустила фирма Control Data Corporation (CDC) при участии одного из ее основателей Суймура Р.Крэя (Seymour R. Cray)

Компьютер CDC 7600 (1969) включал в себя 8 независимых конвейерных устройств, поэтому в нем соединились преимущества конвейерных и суперскалярных ЭВМ.

ILLIAC IV (1974): матричные процессоры. Проект включал в себя сделать 256 процессорных элементов (ПЭ) и разбить их на 4 квадранта по 64 ПЭ, и предусмотреть возможность перестройки в 2 квадранта по 128 ПЭ или 1 квадрант из 256 ПЭ, ткт 40 нс, производительность 1 Гфлоп. Начались работы в 1967 году, к концу 1971 изготовлена система из 1-го квадранта, в 1974 г. она введена в эксплуатацию, доводка велась до 1975 года. Из-за того, что стоимость проекта была в 4 раза выше, сделан лишь 1 квадрант, такт 80нс, реальная производительность до 50 Мфлоп. Но даже при неудачном завершение проекта, данная разработка использовалась при построении серии других суперкомпьютеров.

CRAI 1 (1976): векторно-конвейерные процессоры, создателем которых является компания Cray Research. Время такта 12.5 нс, 12 ковейерных функциональных устройств, пиковая производительность 160 миллионов операций в секунду, оперативная память до 1 Мслова (слово – 64 разряда), цикл памяти 50нс. Самым главным нововведением является включение векторных команд, работающих с целыми массивами независимых данных, которые позволяют эффективно использовать конвейерные функциональные устройства.

Самые первые суперскалярные процессоры фирмы Intel включали в себя два параллельных блока для выполнения операций, первый блок для выполнения произвольных операций, второй – для выполнения только простых операций. Одновременное использование обоих блоков в этом случае было осуществимо только при «правильной» последовательности команд в программе, что при решении конкретных задач практически невозможно. Именно поэтому по возможности компиляторы упорядочивали команды программы таким образом, чтобы максимально использовать оба блока. Тогда и появился режим оптимизации программ, который зависит от используемого процессора.

На сегодняшний момент процессоры суперскалярные и содержат разное число специализированых блоков, к примеру, блоки для выполнения арифметических операций, операций с плавающей точкой.

Параллелизм на уровне данных. SIMD команды

Очень часто, при решении практических задач приходится для множества данных выполнять одну и ту же операцию. В данном случае можно использовать суперскалярность процессоров, но именно для этого случая современные процессоры имеют специальные команды. В соответствии с их назначением они относятся к группе Single Instruction Multiple Data – одна команда для множества данных (SIMD). Векторно-конвейерными называются компьютеры, которые вместе с конвейером обеспечивают возможность одновременной обработки сразу целого массива. Обычно SIMD команды реализуются с помощью специального конвейера, из-за этого могут выполняться одновременно с основным потоком команд. Представителем данного направления является семейство векторно-конвейерных компьютеров CRAY. Для персональных компьютеров ограничен размер блока 128 битами. Блок может интерпретироваться как массив байтов, 2-байтовых и 4-байтовых слов, а также двух данных длинной 8 байтов, и, наконец, одного блока длинной 16 байтов. Набор команд, а также интерпретация данных (целые, с плавающей точкой) все время расширяется. На сегодня для персональных компьютеров используется несколько классов команд этой группы (MMX – Multi Media Extensions., 3DNow, SSE – Streaming SIMD Extension) разных версий. SIMD команды позволяют распараллелить обработку множества данных без накладных расходов. На сегодняшний момент применение этих команд упрощено в связи с возможностью их использования в С программе.

Пример применения операции сложения для массивов целых чисел, состоящих из четырех чисел:

//Выделение памяти и инициализация массивов

__declspec (align(16))

int x[]={1,2,3,4},

y[]={5,6,7,8},

z=[4];

//Сложение элементов массивов

*(__m128i*)z=_mm_add_epi32(*(__m128i*)x,*(__m128i*)y);

printf(«%d%d%d%dn»,z[0],z[1],z[2],z[3]);

Для сложения чисел фактически выполняется следующие команды:

- загрузка первого массива в 128-битный регистр (т.е. сразу 4-х слагаемых);

- загрузка второго массива в 128-битный регистр (т.е. сразу 4-х слагаемых);

- сложение всех элементов массива (одна команда);

- запись результата в массив.

Параллелизм на уровне задач

Понятие «задача» имеет разный смысл. Если рассматривать процессоров, задачей является программа во время выполнения, а переключение между задачами, это переключение между этими программами, которое инициируется операционной системой и может быть: при истечении кванта времени, если задача ждет выполнения запроса, если требуется выполнения более привилегированных задач. Рассматривая операционные системы, вместо термина задача можно использовать термин процесс, в который фактически вкладывается тот же смысл. Именно поэтому параллелизм на уровне задач предполагает возможность параллельного выполнения отдельных программ. Также наряду с обычными процессами, которым соответствует программа, операционные системы для параллельного выполнения могут использовать отдельных функции процесса (потоки). Рассмотрим параллелизм на уровне процессов и потоков. В этом случае при использовании одного одноядерного процессора может выполняться одновременно только одна функция одного процесса. При режиме разделения времени и высокой скорости выполнения команд может показаться одновременное выполнение, но это не так. Фактически при переключении между потоками старый поток блокируется.

В системах с одни ядром и без Hyper-Threading (HT) технологии в исполнении команд участвует исполнительный блок и внутренний Кеш. Эти элементы вычислительной системы можно назвать вычислительным блоком. Для многопроцессорных систем, вычислительная система имеет несколько вычислительных блоков. Для систем с НТ технологией фактически входит один исполнительный блок, который имеет вид двух логических блоков за счет того, что дублируются некоторые его части (регистры). В многоядерной системе используется несколько вычислительных систем, расположенных физически внутри одной схемы. Многоядерные системы могут использовать как общий внутренний Кеш, так и каждое ядро свой Кеш. Возможна комбинация многоядерности и НТ.

В НТ технологии все ресурсы вычислительного блока (одного) делятся между исполняемыми потоками операционной системой. К примеру, если один поток ждет ввода – вывода данных, то второй поток выполняется с помощью вычислительного блока. Все логические блоки имеют свою копию регистров, поэтому переключения состояния фактически не потребуется, как это в обычных однопроцессорных системах. Общий эффект существенно зависит от потоков, которые работают в паре. При том что все потоки используют одни и те же ресурсы, эффекта фактически не будет, так как устройство одно.

Чтобы достичь истинно параллельного выполнения функций следует иметь несколько процессоров или несколько ядер процессора.

Появление многоядерных процессоров фактически сделало доступными высокопроизводительные вычисления (High Performance Computing – HPC) на домашних компьютерах.

То есть в одной микросхеме располагаются теперь несколько полноценных и равноправных процессорных устройств. Данная технология применяется как в недорогих процессорах (Intel Core 2, AMD Athlon), так и в процессорах для мощных рабочих станций и серверов (AMD Opteron, Intel Xeon). Количество ядер все время растет. На сегодняшний день используются процессоры с 2, 4 и 8 ядрами, в стадии исследования и разработки находятся процессоры с десятками и сотнями ядер, поэтому распараллеливание и масштабирование (т.е. распределение между всеми ядрами процессора) приложений является сложной как теоретической, так и практической задачей, которая на данный момент пока не решена в полной мере.

Память и параллелизм

Как известно, выполнение команд происходит гораздо значительно быстрее, чем доступ к памяти. Чтобы уменьшить потери, связанные с разной скоростью доступа, используется многоуровневая память. Существуют несколько уровней памяти, которые задаются в порядке увеличения времени доступа: регистры, Кеш-память (несколько уровней), оперативная память, внешняя память. Обеспечение параллелизма осуществляется за счет того, что во время выполнения команд и обработки данных используется регистровая и Кеш-память первого уровня, заполняющиеся данными до того, пока они будут использоваться, и до момента, когда они будут нужны, они, как правило, уже находятся в нужной памяти (если конечно, число команд перехода минимизировано!)

Следует рассмотреть классические архитектуры систем с параллельной обработкой данных и команд с точки зрения использования памяти.

Массивно-параллельные компьютеры (MPP)

Данная система включает в себя несколько компьютеров со своей локальной памятью соединяются в одну вычислительную систему с помощью коммутационных устройств [6].

Система состоит из однородных вычислительных узлов, включающих:

- один или несколько центральных процессоров (обычно RISC);

- локальную память (прямой доступ к памяти других узлов невозможен);

- коммуникационный процессор или сетевой адаптер;

- иногда – жесткие диски (как в SP) и/или другие устройства I/O.

Примеры: IBM RS/6000 SP2, Intel PARAGON/ASCI Red, CRAY T3E, Hitachi SR 8000, транспьютерные системы Parsytec.

Достоинством данной архитектуры можно считать возможность ее расширения. Недостаток является медленная передача данных между компьютерами. На сегодняшний момент коммуникационные устройства уменьшают потери, которые связаны с передачей данных, но в любом случае эта операция значительно медленнее, чем при использовании своей памяти.

Симметричные мультипроцессорные системы (SMP – Symmetrical Multi Processor systems)

Одинаковые процессоры подключаются к общей памяти, при этом скорость обращения к общей памяти для всех процессоров одинакова. Процессоры подключаются к памяти либо с помощью общей шины (базовые 2-4-х процессорные SMP-серверы), либо с помощью crossbar-коммутатора (HP 9000). Аппаратно поддерживается когерентность Кешей (гарантия использования актуального значения, данного независимо от того, в каком Кеше изменено его значение). Хоть и проблема передачи данных между памятью решается автоматически, остается ещё одна, это подключение процессоров к общей памяти. Количество процессоров, которые можно подключить, обычно невелико, около 2-4 устройства. Использование 32-х устройств очень дорого, стоимость такой вычислительной системы сотни тысяч долларов.

В связи с использованием общей памяти необходима синхронизация и блокировка в случае попытки доступа к занятому ресурсу с эксклюзивным доступом.

Примеры: HP 9000 V-class, N-class; SMP-сервер и рабочие станции на базе процессоров Intel(IBM, HP,Compaq, Dell, ALR, Unisys, DG, Fujitsu и др.).

Системы с неоднородным доступом к памяти (NUMA – Non-Uniform Memory Access systems)

Состоит система из однородных базовых модулей (плат), которые имеют в своём составе небольшое число процессоров и блок памяти. Объединены модули с помощью высокоскоростного коммутатора. Обеспечивается поддержка единого адресного пространства, аппаратно поддерживается доступ к удаленной памяти, т.е. к памяти других модулей. Доступ к локальной памяти в несколько раз быстрее, чем к удаленной, а скорость доступа к удаленной памяти будет больше, чем дальше будет удалена память от процессора.

В случае если аппаратно поддерживается когерентность Кешей во всей системе (обычно это так), говорят об архитектуре cc-NUMA (cache-coherent NUMA).

В случае попытки доступа к занятому ресурсу с эксклюзивным доступом, при использование общей памяти, необходима синхронизация и блокировка. Также при разработке алгоритма желательно обеспечить доступ к «своей» памяти везде, где есть возможно.

Примеры: Примеры: HP 9000 V-class в SCA-конфигурациях, SGI Origin2000, Sun HPC 10000, IBM/Sequent NUMA-Q 2000, SNI RM600.

Параллельные векторные системы (PVP)

Главным признаком PVP-систем можно считать наличие специальных векторно-конвейерных процессоров, которые имеют команды однотипной обработки векторов независимых данных, которые эффективно выполняются на конвейерных функциональных устройствах.

В основном, несколько таких процессоров (1-16) работают одновременно над общей памятью (аналогично SMP) в многопроцессорных конфигурациях. Объединение несколько узлов происходит с помощью коммутатора (аналогично MPP).

Примеры: NEC SX-4/SX-5, линия векторно-конвейерных компьютеров CRAY: от CRAY-1, CRAY J90/T90, CRAY SV1, CRAY X1, серия Fujitsu VPP.

Кластерные системы

В качестве дешевого варианта массивно-параллельного компьютера используется набор рабочих станций (или даже ПК) общего назначения. Что узлы имели связь используется одна из стандартных сетевых технологий (Fast/Gigabit Ethernet, Myrinet) на базе шинной архитектуры или коммутатора.

Когда происходит объединении в кластер компьютеров разной мощности или разной архитектуры говорят о гетерогенных (неоднородных) кластерах.

Узлы кластера можно одновременно использовать в качестве пользовательских рабочих станций. Если это не нужно, узлы можно существенно облегчить и/или установить в стойку.

Актуальной проблемой является доступа к «чужой» памяти, из-за этого часто такая система используется для одновременного решения нескольких независимых задач.

Примеры: NT-кластер в NCSA, Beowulf-кластеры.

Многоядерные процессоры

С точки зрения программиста, многоядерным процессором является несколько процессоров, имеющие раздельный Кеш 0 уровня (Кеш 2-го и более высоких уровней чаще общий, но может быть и раздельным) и общую оперативную память. По этой причине желательно при разработке алгоритмов обеспечивать максимальную независимость данных, которые используются в разных ядрах. Синхронизация и блокировка являются на данный момент актуальной проблемой.

Используемая литература:

- Flynn M. Very high-speed computing system // Proc. IEEE. 1966. N 54. P.1901-1909.

- Hwang K., Briggs F.A. Computer Architecture and Parallel Processing. 1984. P.32-40.

- http://ru.wikipedia.org/wiki/Параллельные_вычисления; http://ru.wikipedia.org/wiki/Нейрокомпьютер ;

- Гергелъ В.П., Стронгин Р.Г Основы параллельных вычислений для многопроцессорных вычислительных систем. Нижний Новгород: -Издательство Нижегородского госуниверситета, 2003

- Воеводин В.В., Воеводин Вл.в. Параллельные вычисления. СПб: БХВ – Петербург, 2004 – 608с.

Большое разнообразие

структур ВС затрудняет их изучение.

Поэтому вычислительные системы

классифицируют с учетом их обобщенных

характеристик. С этой целью вводится

понятие «архитектура системы».

Архитектура

ВС —

совокупность

характеристик и параметров, определяющих

функционально-логическую и структурную

организацию системы. Понятие

архитектуры охватывает общие принципы

построения и функционирования, наиболее

существенные для пользователей,

которых больше интересуют возможности

систем, а не детали их технического

исполнения. Поскольку ВС появились как

параллельные системы, то и рассмотрим

классификацию архитектур под этой

точкой зрения.

Эта

классификация архитектур была предложена

М. Флинном (М. Flynn)

в начале 60-х гг. В ее основу заложено два

возможных вида параллелизма: независимость

потоков заданий (команд), существующих

в системе, и независимость

(несвязанность) данных, обрабатываемых

в каждом потоке. Классификация до

настоящего времени еще не потеряла

своего значения. Однако подчеркнем,

что, как и любая классификация, она

носит временный и условный характер.

Своим долголетием она обязана тому,

что оказалась справедливой для ВС, в

которых ЭВМ и процессоры реализуют

программные последовательные методы

вычислений. С появлением систем,

ориентированных на потоки данных и

использование ассоциативной обработки,

данная классификация может быть

некорректной.

Согласно этой

классификации существует четыре основных

архитектуры ВС, представленных на

рис. 11.3:

• одиночный

поток команд — одиночный поток данных

(ОКОД), в английском варианте — Single

Instruction

Single

Data

(SISD)

— одиночный поток инструкций —

одиночный поток данных;

• одиночный

поток команд — множественный поток

данных (ОКМД), или Single

Instruction

Multiple

Data

(SIMD)

— одиночный поток инструкций — одиночный

поток данных;

• множественный

поток команд — одиночный поток данных

(МКОД), или Multiple

Instruction

Single

Data

(MISD)

— множественный поток инструкций —

одиночный поток данных;

• множественный

поток команд — множественный поток

данных (МКМД), или Multiple

Instruction

Multiple

Data

(MIMD)

— множественный поток инструкций —

множественный поток данных (MIMD).

Рис.

11.3. Архитектура

ВС: а

— ОКОД

(SISD)-архитектура;

б—

ОКМД

(SIМD)-архитектура;

в

— МКОД

(МISD)-архитектура;

г —

МКМД

(МIMD)-архитектура

Коротко рассмотрим

отличительные особенности каждой из

архитектур.

Архитектура

ОКОД охватывает

все однопроцессорные и одномашинные

варианты систем, т.е. с одним вычислителем.

Все ЭВМ классической структуры попадают

в этот класс. Здесь параллелизм вычислений

обеспечивается путем совмещения

выполнения операций отдельными блоками

АЛУ, а также параллельной работы устройств

ввода-вывода информации и процессора.

Закономерности организации

вычислительного процесса в этих

структурах достаточно хорошо изучены.

Архитектура

ОКМД предполагает

создание структур векторной или

матричной обработки. Системы этого типа

обычно строятся как однородные, т.е.

процессорные, элементы, входящие в

систему, идентичны, и все они управляются

одной и той же последовательностью

команд. Однако каждый процессор

обрабатывает свой поток данных. Под эту

схему хорошо подходят задачи обработки

матриц или векторов (массивов), задачи

решения систем линейных и нелинейных,

алгебраических и дифференциальных

уравнений, задачи теории поля и др.

В структурах данной архитектуры

желательно обеспечивать соединения

между процессорами, соответствующие

реализуемым математическим зависимостям.

Как правило, эти связи напоминают

матрицу, в которой каждый процессорный

элемент связан с соседними.

По

этой схеме строились системы: первая

суперЭВМ — ILLIAC-IV,

отечественные параллельные системы —

ПС-2000, ПС-3000. Идея векторной обработки

широко использовалась в таких известных

суперЭВМ, как Cyber-205

и Gray-I,

II,

III.

Узким местом подобных систем является

необходимость изменения коммутации

между процессорами, когда связь между

ними отличается от матричной. Кроме

того, задачи, допускающие широкий

матричный параллелизм, составляют

достаточно узкий класс задач. Структуры

ВС этого типа, по существу, являются

структурами специализированных суперЭВМ.

Третий

тип архитектуры МКОД предполагает

построение своеобразного процессорного

конвейера, в котором результаты обработки

передаются от одного процессора к

другому по цепочке. Выгоды такого вида

обработки понятны. Прототипом таких

вычислений может служить схема любого

производственного конвейера. В

современных ЭВМ по этому принципу

реализована схема совмещения операций,

в которой параллельно работают различные

функциональные блоки, и каждый из них

делает свою часть в общем цикле обработки

команды.

В ВС этого типа

конвейер должны образовывать группы

процессоров. Однако при переходе на

системный уровень очень трудно выявить

подобный регулярный характер в

универсальных вычислениях. Кроме

того, на практике нельзя обеспечить и

«большую длину» такого конвейера, при

которой достигается наивысший эффект.

Вместе с тем конвейерная схема нашла

применение в так называемых скалярных

процессорах суперЭВМ, в которых они

применяются как специальные процессоры

для поддержки векторной обработки.

Архитектура

МКМД предполагает,

что все процессоры системы работают

по своим программам с собственным

потоком команд. В простейшем случае они

могут быть автономны и независимы. Такая

схема использования ВС часто применяется

на многих крупных вычислительных

центрах для увеличения пропускной

способности центра. Больший интерес

представляет возможность согласованной

работы ЭВМ (процессоров), когда каждый

элемент делает часть общей задачи. Общая

теоретическая база такого вида работ

практически отсутствует. Но можно

привести примеры большой эффективности

этой модели вычислений. Подобные системы

могут быть многомашинными и

многопроцессорными. Например,

отечественный проект машины

динамической архитектуры (МДА) — ЕС-2704,

ЕС-2127

— позволял

одновременно использовать сотни

процессоров.