Конфигурация PINCTRL

Конфигурация платформы Qualcomm Группа I2S, как правило, соответствует четыре или шести GPIO,

Quin MI2S соответствует gpio88 gpio91 gpio92 gpio93

Соответствующий файл кода: ядро / MSM-3.18 / Arch / ARM / BOOT / BOOT / DTS / QCOM / MSM8953-PINCTRL.DTSI

pri-tlmm-lines {

pri_tlmm_lines_act: pri_tlmm_lines_act {

mux {

pins = "gpio91", "gpio88", "gpio93";

function = "pri_mi2s";

};

config {

pins = "gpio91", "gpio88", "gpio93";

drive-strength = <8>;

};

};

pri_tlmm_lines_sus: pri_tlmm_lines_sus {

mux {

pins = "gpio91", "gpio88", "gpio93";

function = "pri_mi2s";

};

config {

pins = "gpio91", "gpio88", "gpio93";

drive-strength = <2>;

bias-pull-down;

};

};

};Настройка PINCTRL также необходимо подключить к узлу звуковой карты.

Изменение файла: ядро / MSM-3.18 / ARCH / ARM / BOOT / BOOT / DTS / QCOM / MSM8953-AUDIO.DTSI

qcom,msm-gpios =

"pri_i2s",

"quin_i2s";

qcom,pinctrl-names =

"all_off",

"pri_i2s_act",

"quin_act",

"quin_pri_i2s_act";

pinctrl-names =

"all_off",

"pri_i2s_act",

"quin_act",

"quin_pri_i2s_act";

pinctrl-0 = <&cdc_pdm_lines_sus &cdc_pdm_lines_2_sus &pri_tlmm_lines_sus &pri_tlmm_ws_sus>;

pinctrl-1 = <&cdc_pdm_lines_act &cdc_pdm_lines_2_act &pri_tlmm_lines_sus &pri_tlmm_ws_sus>;

pinctrl-2 = <&cdc_pdm_lines_sus &cdc_pdm_lines_2_sus &pri_tlmm_lines_act &pri_tlmm_ws_act>;

pinctrl-3 = <&cdc_pdm_lines_act &cdc_pdm_lines_2_act &pri_tlmm_lines_act &pri_tlmm_ws_act>;2. Зарегистрируйте конфигурацию

Узнайте на документе Qualcomm MSM8953 внешний обзор интерфейса MI2S для настройки следующих регистров MI2S для настройки следующих регистров.

Итак, как вы настраиваете эти регистры в вашем коде? Это должно быть изменено в следующие файлы.

Изменить файл:

kernel/msm-3.18/sound/soc/msm/msm8952.c

kernel/msm-3.18/sound/soc/codecs/msm8x16-wcd.h

kernel/msm-3.18/arch/arm/boot/dts/qcom/msm-audio.dtsi

Там, где настроено ядро / MSM-3.18 / Arch / Arm / Boot / DTS / QCOM / MSM-Audio.dtsi Конфигурация:

int_codec: sound {

compatible = "qcom,msm8952-audio-codec";

//added by kuangjincheng @20171221

reg = <0xc051000 0x4>,//LPASS_CSR_GP_IO_MUX_MIC_CTL

<0xc051004 0x4>,//LPASS_CSR_GP_IO_MUX_SPKR_CTL

<0xc055000 0x4>,//LPASS_CSR_GP_LPAIF_PRI_PCM_PRI_MODE_MUXSEL

<0xc052000 0x4>,//LPASS_ CSR_GP_IO_MUX_QUI_CTL

<0xc054000 0x4>,//LPASS_CSR_GP_IO_MUX_MIC_EXT_CLK_CTL

<0xc056000 0x4>,// LPASS_CSR_GP_LPAIF_QUI_PCM_SEC_MODE_MUXSEL

<0xc054008 0x4>;//LPASS_CSR_GP_IO_MUX_QUI_EXT_CLK_CTL

reg-names = "csr_gp_io_mux_mic_ctl",

"csr_gp_io_mux_spkr_ctl",

"csr_gp_io_lpaif_pri_pcm_pri_mode_muxsel",

"csr_gp_io_mux_quin_ctl",

"csr_gp_io_mux_mic_ext_clk_ctl",

"csr_gp_io_lpaif_qui_pcm_sec_mode_muxsel",

"csr_gp_io_mux_quin_ext_clk_ctl";

};В структуре устройства в заголовочном файле ядра / MSM-3.18 / SOUND / SOC / CODECS / MSM8X16-WCD.H добавляется элемент указателя, а адрес регистра сохраняется.

struct msm8916_asoc_mach_data {

int codec_type;

int ext_pa;

int us_euro_gpio;

int spk_ext_pa_gpio;

int mclk_freq;

int lb_mode;

int afe_clk_ver;

u8 micbias1_cap_mode;

u8 micbias2_cap_mode;

atomic_t mclk_rsc_ref;

atomic_t mclk_enabled;

atomic_t wsa_mclk_rsc_ref;

struct mutex cdc_mclk_mutex;

struct mutex wsa_mclk_mutex;

struct delayed_work disable_mclk_work;

struct afe_digital_clk_cfg digital_cdc_clk;

struct afe_clk_set digital_cdc_core_clk;

void __iomem *vaddr_gpio_mux_spkr_ctl;

void __iomem *vaddr_gpio_mux_mic_ctl;

void __iomem *vaddr_gpio_mux_quin_ctl;

void __iomem *vaddr_gpio_mux_pcm_ctl;

//added by kuangjincheng @20171221 QUAT_MI2S_SLAVE_MODE config

void __iomem *vaddr_gpio_mux_mic_ext_clk_ctl;

//added by kuangjincheng @20180521 QUIN_MI2S_SLAVE_MODE config

void __iomem *vaddr_gpio_quin_sec_muxsel;

void __iomem *vaddr_gpio_mux_quin_ext_clk_ctl;

struct on_demand_supply wsa_switch_supply;

};В функции MSM8952_ASOC_Machine_probe из ядра / MSM / MSM8952.C соответствующий адрес регистра анализируется и сохранен на элементах, соответствующих структуре устройства.

//added by kuangjincheng @20180521 QUIN_MI2S_SLAVE_MODE config

muxsel = platform_get_resource_byname(pdev, IORESOURCE_MEM, "csr_gp_io_lpaif_qui_pcm_sec_mode_muxsel");

if (!muxsel) {

dev_dbg(&pdev->dev, "MUX addr invalid for MI2Sn");

goto parse_mclk_freq;

}

pdata->vaddr_gpio_quin_sec_muxsel = ioremap(muxsel->start, resource_size(muxsel));

if (pdata->vaddr_gpio_quin_sec_muxsel == NULL) {

pr_err("%s ==4ioremap failure for muxsel virt addrn", __func__);

ret = -ENOMEM;

goto err;

}

muxsel = platform_get_resource_byname(pdev, IORESOURCE_MEM, "csr_gp_io_mux_quin_ext_clk_ctl");

if (!muxsel) {

dev_dbg(&pdev->dev, "MUX addr invalid for MI2Sn");

goto parse_mclk_freq;

}

pdata->vaddr_gpio_mux_quin_ext_clk_ctl = ioremap(muxsel->start, resource_size(muxsel));

if (pdata->vaddr_gpio_mux_quin_ext_clk_ctl == NULL) {

pr_err("%s ==5ioremap failure for muxsel virt addrn", __func__);

ret = -ENOMEM;

goto err;

}Конфигурация регистров имеет последний шаг — выполнить конфигурацию регистров в I2S, соответствующих MSM_QUIN_MI2S_SND_STARTUP.

static int msm_quin_mi2s_snd_startup(struct snd_pcm_substream *substream)

{

struct snd_soc_pcm_runtime *rtd = substream->private_data;

struct snd_soc_card *card = rtd->card;

struct snd_soc_dai *cpu_dai = rtd->cpu_dai;

struct msm8916_asoc_mach_data *pdata =

snd_soc_card_get_drvdata(card);

int ret = 0, val = 0;

pr_err("honeywell_msm8952>>>%s: substream = %s stream = %dn", __func__, substream->name, substream->stream);

#ifdef QUIN_MI2S_USE_SLAVE_MODE

//0xc051000 LPASS_CSR_GP_IO_MUX_MIC_CTL

if(pdata->vaddr_gpio_mux_mic_ctl){

val = ioread32(pdata->vaddr_gpio_mux_mic_ctl);

val = 0x00000000;

iowrite32(val, pdata->vaddr_gpio_mux_mic_ctl);

}

pr_err("msm8952>>>%s: iowrite32 vaddr_gpio_mux_mic_ctln", __func__);

//0xc056000 LPASS_CSR_GP_LPAIF_QUI_PCM_SEC_MODE_MUXSEL

if(pdata->vaddr_gpio_quin_sec_muxsel){

val = ioread32(pdata->vaddr_gpio_quin_sec_muxsel);

val = 0x00000000;

iowrite32(val, pdata->vaddr_gpio_quin_sec_muxsel);

}

pr_err("msm8952>>>%s: iowrite32 vaddr_gpio_quin_sec_muxseln", __func__);

//0xc052000 LPASS_ CSR_GP_IO_MUX_QUI_CTL

if(pdata->vaddr_gpio_mux_quin_ctl){

val = ioread32(pdata->vaddr_gpio_mux_quin_ctl);

val = 0x00000001;

iowrite32(val, pdata->vaddr_gpio_mux_quin_ctl);

}

pr_err("msm8952>>>%s: iowrite32 vaddr_gpio_mux_quin_ctln", __func__);

//0xc054008 LPASS_CSR_GP_IO_MUX_QUI_EXT_CLK_CTL

if(pdata->vaddr_gpio_mux_quin_ext_clk_ctl){

val = ioread32(pdata->vaddr_gpio_mux_quin_ext_clk_ctl);

val = 0x00000001;

iowrite32(val, pdata->vaddr_gpio_mux_quin_ext_clk_ctl);

}

pr_err("msm8952>>>%s: iowrite32 vaddr_gpio_mux_quin_ext_clk_ctln", __func__);

#else

if (pdata->vaddr_gpio_mux_quin_ctl) {

val = ioread32(pdata->vaddr_gpio_mux_quin_ctl);

val = val | 0x00000001;

iowrite32(val, pdata->vaddr_gpio_mux_quin_ctl);

} else {

return -EINVAL;

}

#endif

pr_err("honeywell_msm8952>>>%s: ---001n", __func__);

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = msm_quin_i2s_sclk_ctl(substream, true);

#else

ret = msm_mi2s_sclk_ctl(substream, true);

#endif

if (ret < 0) {

pr_err("honeywell_msm8952>>>%s: failed to enable sclkn", __func__);

return ret;

}

pr_err("honeywell_msm8952>>>%s: ---002n", __func__);

ret = msm_gpioset_activate(CLIENT_WCD_INT, "quin_i2s");

if (ret < 0) {

pr_err("honeywell_msm8952>>>%s: failed to enable codec gpiosn", __func__);

goto err;

}

pr_err("honeywell_msm8952>>>%s: ---003n", __func__);

if (atomic_inc_return(&quin_mi2s_clk_ref) == 1) {

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = snd_soc_dai_set_fmt(cpu_dai, SND_SOC_DAIFMT_CBM_CFM);

#else

ret = snd_soc_dai_set_fmt(cpu_dai, SND_SOC_DAIFMT_CBS_CFS);

#endif

if (ret < 0)

pr_err("honeywell_msm8952>>>%s: set fmt cpu dai failedn", __func__);

}

pr_err("honeywell_msm8952>>>%s: ---004n", __func__);

return ret;

err:

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = msm_quin_i2s_sclk_ctl(substream, false);

#else

ret = msm_mi2s_sclk_ctl(substream, false);

#endif

if (ret < 0)

pr_err("failed to disable sclkn");

return ret;

}

static void msm_quin_mi2s_snd_shutdown(struct snd_pcm_substream *substream)

{

int ret;

pr_err("honeywell_msm8952>>>%s: substream = %s stream = %dn", __func__, substream->name, substream->stream);

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = msm_quin_i2s_sclk_ctl(substream, false);

#else

ret = msm_mi2s_sclk_ctl(substream, false);

#endif

if (ret < 0)

pr_err("honeywell_msm8952>>>%s: clock disable failedn", __func__);

if (atomic_read(&quin_mi2s_clk_ref) > 0)

atomic_dec(&quin_mi2s_clk_ref);

ret = msm_gpioset_suspend(CLIENT_WCD_INT, "quin_i2s");

if (ret < 0) {

pr_err("honeywell_msm8952>>>%s: gpio set cannot be de-activated %sd", __func__, "quin_i2s");

return;

}

}3. Конфигурация часов

(1) Кто дает часы?

Часы в конфигурации часов обеспечиваются MSM8953 или сторонним чипом кодека, который обеспечивается внешним кристаллом, который напрямую связан с основным подчиненным режимом I2S.

Когда I2S является основным режимом, часы имеют внутренний хрустальный генератор MSM8953; наоборот, он предоставляется третьим сторонним кодеком.

Код, настроенный здесь, также установлен в функции MSM_QUIN_MI2S_SND_STARTUP.

Соответствующий сегмент кода индивидуально перехвачен:

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = snd_soc_dai_set_fmt(cpu_dai, SND_SOC_DAIFMT_CBM_CFM);

#else

ret = snd_soc_dai_set_fmt(cpu_dai, SND_SOC_DAIFMT_CBS_CFS);

#endif(2) Как так часто частота настройки?

Здесь MSM_MI2S_SCLK_CTL записывает функцию MSM_QUIN_I2S_SCLK_CTL для конфигурации часов рабочего режима.

//added by kuangjincheng @20180521 QUIN_MI2S_SLAVE_MODE config

#ifdef QUIN_MI2S_USE_SLAVE_MODE

static struct afe_clk_set quin_i2s_rx_clk = {

AFE_API_VERSION_I2S_CONFIG,

Q6AFE_LPASS_CLK_ID_QUI_MI2S_EBIT,

Q6AFE_LPASS_OSR_CLK_1_P536_MHZ,

Q6AFE_LPASS_CLK_ATTRIBUTE_COUPLE_NO,

Q6AFE_LPASS_CLK_ROOT_DEFAULT,

0,

};

static struct afe_clk_set quin_i2s_tx_clk = {

AFE_API_VERSION_I2S_CONFIG,

Q6AFE_LPASS_CLK_ID_QUI_MI2S_EBIT,

Q6AFE_LPASS_OSR_CLK_3_P072_MHZ,

Q6AFE_LPASS_CLK_ATTRIBUTE_COUPLE_NO,

Q6AFE_LPASS_CLK_ROOT_DEFAULT,

0,

};

#endif

//added by kuangjincheng @20180521 QUIN_MI2S_SLAVE_MODE config

#ifdef QUIN_MI2S_USE_SLAVE_MODE

static int msm_quin_i2s_sclk_ctl(struct snd_pcm_substream *substream, bool enable)

{

int ret = 0;

struct snd_soc_pcm_runtime *rtd = substream->private_data;

int port_id = 0;

pr_err("msm8952>>>%s: entern", __func__);

port_id = msm8952_get_port_id(rtd->dai_link->be_id);

if (port_id < 0) {

pr_err("msm8952>>>%s: Invalid port_idn", __func__);

return -EINVAL;

}

if (enable) {

if (substream->stream == SNDRV_PCM_STREAM_PLAYBACK) {

quin_i2s_rx_clk.enable = enable;

quin_i2s_rx_clk.clk_id = msm8952_get_clk_id(port_id);

quin_i2s_rx_clk.clk_freq_in_hz = get_mi2s_rx_clk_val(port_id);

ret = afe_set_lpass_clock_v2(port_id, &quin_i2s_rx_clk);

} else if (substream->stream == SNDRV_PCM_STREAM_CAPTURE) {

quin_i2s_tx_clk.enable = enable;

quin_i2s_tx_clk.clk_id = msm8952_get_clk_id(port_id);

quin_i2s_tx_clk.clk_freq_in_hz = Q6AFE_LPASS_OSR_CLK_1_P536_MHZ;

ret = afe_set_lpass_clock_v2(port_id, &quin_i2s_tx_clk);

} else {

pr_err("msm8952>>>%s: Not valid substream.n", __func__);

}

if (ret < 0)

pr_err("msm8952>>>%s: enable: %d, afe_set_lpass_clock_v2 failedn", __func__, enable);

} else {

if (substream->stream == SNDRV_PCM_STREAM_PLAYBACK) {

quin_i2s_rx_clk.enable = enable;

quin_i2s_rx_clk.clk_id = msm8952_get_clk_id(port_id);

ret = afe_set_lpass_clock_v2(port_id, &quin_i2s_rx_clk);

} else if (substream->stream == SNDRV_PCM_STREAM_CAPTURE) {

quin_i2s_tx_clk.enable = enable;

quin_i2s_tx_clk.clk_id = msm8952_get_clk_id(port_id);

ret = afe_set_lpass_clock_v2(port_id, &quin_i2s_tx_clk);

} else {

pr_err("msm8952>>>%s: Not valid substream.n", __func__);

}

if (ret < 0)

pr_err("msm8952>>>%s: enable: %d, afe_set_lpass_clock_v2 failedn", __func__, enable);

}

return ret;

}

#endif4. Сводка и расширение

Приведенный выше код модифицирован для завершения шины I2S из конфигурации режима, а основной субклюк-микрофон можно вырезать на макро определение Quin_MI2S_USE_SLAVE_MODE.

Расширенный:

kernel/msm-3.18/include/uapi/sound/asound.h

kernel/msm-3.18/include/sound/apr_audio-v2.h

Формат PCM можно установить:

SNDRV_PCM_FORMAT_S16_LE

SNDRV_PCM_FORMAT_S24_LE

SNDRV_PCM_FORMAT_S24_3LE

Битовые часы могут быть выбраны для:

/* Supported OSR clock values */

#define Q6AFE_LPASS_OSR_CLK_12_P288_MHZ 0xBB8000

#define Q6AFE_LPASS_OSR_CLK_9_P600_MHZ 0x927C00

#define Q6AFE_LPASS_OSR_CLK_8_P192_MHZ 0x7D0000

#define Q6AFE_LPASS_OSR_CLK_6_P144_MHZ 0x5DC000

#define Q6AFE_LPASS_OSR_CLK_4_P096_MHZ 0x3E8000

#define Q6AFE_LPASS_OSR_CLK_3_P072_MHZ 0x2EE000

#define Q6AFE_LPASS_OSR_CLK_2_P048_MHZ 0x1F4000

#define Q6AFE_LPASS_OSR_CLK_1_P536_MHZ 0x177000

#define Q6AFE_LPASS_OSR_CLK_1_P024_MHZ 0xFA000

#define Q6AFE_LPASS_OSR_CLK_768_kHZ 0xBB800

#define Q6AFE_LPASS_OSR_CLK_512_kHZ 0x7D000

#define Q6AFE_LPASS_OSR_CLK_DISABLE 0x0

/* Supported Bit clock values */

#define Q6AFE_LPASS_IBIT_CLK_12_P288_MHZ 0xBB8000

#define Q6AFE_LPASS_IBIT_CLK_11_P2896_MHZ 0xAC4400

#define Q6AFE_LPASS_IBIT_CLK_8_P192_MHZ 0x7D0000

#define Q6AFE_LPASS_IBIT_CLK_6_P144_MHZ 0x5DC000

#define Q6AFE_LPASS_IBIT_CLK_4_P096_MHZ 0x3E8000

#define Q6AFE_LPASS_IBIT_CLK_3_P072_MHZ 0x2EE000

#define Q6AFE_LPASS_IBIT_CLK_2_P8224_MHZ 0x2b1100

#define Q6AFE_LPASS_IBIT_CLK_2_P048_MHZ 0x1F4000

#define Q6AFE_LPASS_IBIT_CLK_1_P536_MHZ 0x177000

#define Q6AFE_LPASS_IBIT_CLK_1_P4112_MHZ 0x158880

#define Q6AFE_LPASS_IBIT_CLK_1_P024_MHZ 0xFA000

#define Q6AFE_LPASS_IBIT_CLK_768_KHZ 0xBB800

#define Q6AFE_LPASS_IBIT_CLK_512_KHZ 0x7D000

#define Q6AFE_LPASS_IBIT_CLK_256_KHZ 0x3E800

#define Q6AFE_LPASS_IBIT_CLK_DISABLE 0x0Глубина местоположения может быть выбрана: 16, 24

Скорость образца может быть выбрана для:

#define BTSCO_RATE_8KHZ 8000

#define BTSCO_RATE_16KHZ 16000

#define SAMPLING_RATE_48KHZ 48000

#define SAMPLING_RATE_96KHZ 96000

#define SAMPLING_RATE_192KHZ 192000

Эта часть этого раздела находится в документах Qualcomm следующим образом:

Конфигурация PINCTRL

Конфигурация платформы Qualcomm Группа I2S, как правило, соответствует четыре или шести GPIO,

Quin MI2S соответствует gpio88 gpio91 gpio92 gpio93

Соответствующий файл кода: ядро / MSM-3.18 / Arch / ARM / BOOT / BOOT / DTS / QCOM / MSM8953-PINCTRL.DTSI

pri-tlmm-lines {

pri_tlmm_lines_act: pri_tlmm_lines_act {

mux {

pins = "gpio91", "gpio88", "gpio93";

function = "pri_mi2s";

};

config {

pins = "gpio91", "gpio88", "gpio93";

drive-strength = <8>;

};

};

pri_tlmm_lines_sus: pri_tlmm_lines_sus {

mux {

pins = "gpio91", "gpio88", "gpio93";

function = "pri_mi2s";

};

config {

pins = "gpio91", "gpio88", "gpio93";

drive-strength = <2>;

bias-pull-down;

};

};

};Настройка PINCTRL также необходимо подключить к узлу звуковой карты.

Изменение файла: ядро / MSM-3.18 / ARCH / ARM / BOOT / BOOT / DTS / QCOM / MSM8953-AUDIO.DTSI

qcom,msm-gpios =

"pri_i2s",

"quin_i2s";

qcom,pinctrl-names =

"all_off",

"pri_i2s_act",

"quin_act",

"quin_pri_i2s_act";

pinctrl-names =

"all_off",

"pri_i2s_act",

"quin_act",

"quin_pri_i2s_act";

pinctrl-0 = <&cdc_pdm_lines_sus &cdc_pdm_lines_2_sus &pri_tlmm_lines_sus &pri_tlmm_ws_sus>;

pinctrl-1 = <&cdc_pdm_lines_act &cdc_pdm_lines_2_act &pri_tlmm_lines_sus &pri_tlmm_ws_sus>;

pinctrl-2 = <&cdc_pdm_lines_sus &cdc_pdm_lines_2_sus &pri_tlmm_lines_act &pri_tlmm_ws_act>;

pinctrl-3 = <&cdc_pdm_lines_act &cdc_pdm_lines_2_act &pri_tlmm_lines_act &pri_tlmm_ws_act>;2. Зарегистрируйте конфигурацию

Узнайте на документе Qualcomm MSM8953 внешний обзор интерфейса MI2S для настройки следующих регистров MI2S для настройки следующих регистров.

Итак, как вы настраиваете эти регистры в вашем коде? Это должно быть изменено в следующие файлы.

Изменить файл:

kernel/msm-3.18/sound/soc/msm/msm8952.c

kernel/msm-3.18/sound/soc/codecs/msm8x16-wcd.h

kernel/msm-3.18/arch/arm/boot/dts/qcom/msm-audio.dtsi

Там, где настроено ядро / MSM-3.18 / Arch / Arm / Boot / DTS / QCOM / MSM-Audio.dtsi Конфигурация:

int_codec: sound {

compatible = "qcom,msm8952-audio-codec";

//added by kuangjincheng @20171221

reg = <0xc051000 0x4>,//LPASS_CSR_GP_IO_MUX_MIC_CTL

<0xc051004 0x4>,//LPASS_CSR_GP_IO_MUX_SPKR_CTL

<0xc055000 0x4>,//LPASS_CSR_GP_LPAIF_PRI_PCM_PRI_MODE_MUXSEL

<0xc052000 0x4>,//LPASS_ CSR_GP_IO_MUX_QUI_CTL

<0xc054000 0x4>,//LPASS_CSR_GP_IO_MUX_MIC_EXT_CLK_CTL

<0xc056000 0x4>,// LPASS_CSR_GP_LPAIF_QUI_PCM_SEC_MODE_MUXSEL

<0xc054008 0x4>;//LPASS_CSR_GP_IO_MUX_QUI_EXT_CLK_CTL

reg-names = "csr_gp_io_mux_mic_ctl",

"csr_gp_io_mux_spkr_ctl",

"csr_gp_io_lpaif_pri_pcm_pri_mode_muxsel",

"csr_gp_io_mux_quin_ctl",

"csr_gp_io_mux_mic_ext_clk_ctl",

"csr_gp_io_lpaif_qui_pcm_sec_mode_muxsel",

"csr_gp_io_mux_quin_ext_clk_ctl";

};В структуре устройства в заголовочном файле ядра / MSM-3.18 / SOUND / SOC / CODECS / MSM8X16-WCD.H добавляется элемент указателя, а адрес регистра сохраняется.

struct msm8916_asoc_mach_data {

int codec_type;

int ext_pa;

int us_euro_gpio;

int spk_ext_pa_gpio;

int mclk_freq;

int lb_mode;

int afe_clk_ver;

u8 micbias1_cap_mode;

u8 micbias2_cap_mode;

atomic_t mclk_rsc_ref;

atomic_t mclk_enabled;

atomic_t wsa_mclk_rsc_ref;

struct mutex cdc_mclk_mutex;

struct mutex wsa_mclk_mutex;

struct delayed_work disable_mclk_work;

struct afe_digital_clk_cfg digital_cdc_clk;

struct afe_clk_set digital_cdc_core_clk;

void __iomem *vaddr_gpio_mux_spkr_ctl;

void __iomem *vaddr_gpio_mux_mic_ctl;

void __iomem *vaddr_gpio_mux_quin_ctl;

void __iomem *vaddr_gpio_mux_pcm_ctl;

//added by kuangjincheng @20171221 QUAT_MI2S_SLAVE_MODE config

void __iomem *vaddr_gpio_mux_mic_ext_clk_ctl;

//added by kuangjincheng @20180521 QUIN_MI2S_SLAVE_MODE config

void __iomem *vaddr_gpio_quin_sec_muxsel;

void __iomem *vaddr_gpio_mux_quin_ext_clk_ctl;

struct on_demand_supply wsa_switch_supply;

};В функции MSM8952_ASOC_Machine_probe из ядра / MSM / MSM8952.C соответствующий адрес регистра анализируется и сохранен на элементах, соответствующих структуре устройства.

//added by kuangjincheng @20180521 QUIN_MI2S_SLAVE_MODE config

muxsel = platform_get_resource_byname(pdev, IORESOURCE_MEM, "csr_gp_io_lpaif_qui_pcm_sec_mode_muxsel");

if (!muxsel) {

dev_dbg(&pdev->dev, "MUX addr invalid for MI2Sn");

goto parse_mclk_freq;

}

pdata->vaddr_gpio_quin_sec_muxsel = ioremap(muxsel->start, resource_size(muxsel));

if (pdata->vaddr_gpio_quin_sec_muxsel == NULL) {

pr_err("%s ==4ioremap failure for muxsel virt addrn", __func__);

ret = -ENOMEM;

goto err;

}

muxsel = platform_get_resource_byname(pdev, IORESOURCE_MEM, "csr_gp_io_mux_quin_ext_clk_ctl");

if (!muxsel) {

dev_dbg(&pdev->dev, "MUX addr invalid for MI2Sn");

goto parse_mclk_freq;

}

pdata->vaddr_gpio_mux_quin_ext_clk_ctl = ioremap(muxsel->start, resource_size(muxsel));

if (pdata->vaddr_gpio_mux_quin_ext_clk_ctl == NULL) {

pr_err("%s ==5ioremap failure for muxsel virt addrn", __func__);

ret = -ENOMEM;

goto err;

}Конфигурация регистров имеет последний шаг — выполнить конфигурацию регистров в I2S, соответствующих MSM_QUIN_MI2S_SND_STARTUP.

static int msm_quin_mi2s_snd_startup(struct snd_pcm_substream *substream)

{

struct snd_soc_pcm_runtime *rtd = substream->private_data;

struct snd_soc_card *card = rtd->card;

struct snd_soc_dai *cpu_dai = rtd->cpu_dai;

struct msm8916_asoc_mach_data *pdata =

snd_soc_card_get_drvdata(card);

int ret = 0, val = 0;

pr_err("honeywell_msm8952>>>%s: substream = %s stream = %dn", __func__, substream->name, substream->stream);

#ifdef QUIN_MI2S_USE_SLAVE_MODE

//0xc051000 LPASS_CSR_GP_IO_MUX_MIC_CTL

if(pdata->vaddr_gpio_mux_mic_ctl){

val = ioread32(pdata->vaddr_gpio_mux_mic_ctl);

val = 0x00000000;

iowrite32(val, pdata->vaddr_gpio_mux_mic_ctl);

}

pr_err("msm8952>>>%s: iowrite32 vaddr_gpio_mux_mic_ctln", __func__);

//0xc056000 LPASS_CSR_GP_LPAIF_QUI_PCM_SEC_MODE_MUXSEL

if(pdata->vaddr_gpio_quin_sec_muxsel){

val = ioread32(pdata->vaddr_gpio_quin_sec_muxsel);

val = 0x00000000;

iowrite32(val, pdata->vaddr_gpio_quin_sec_muxsel);

}

pr_err("msm8952>>>%s: iowrite32 vaddr_gpio_quin_sec_muxseln", __func__);

//0xc052000 LPASS_ CSR_GP_IO_MUX_QUI_CTL

if(pdata->vaddr_gpio_mux_quin_ctl){

val = ioread32(pdata->vaddr_gpio_mux_quin_ctl);

val = 0x00000001;

iowrite32(val, pdata->vaddr_gpio_mux_quin_ctl);

}

pr_err("msm8952>>>%s: iowrite32 vaddr_gpio_mux_quin_ctln", __func__);

//0xc054008 LPASS_CSR_GP_IO_MUX_QUI_EXT_CLK_CTL

if(pdata->vaddr_gpio_mux_quin_ext_clk_ctl){

val = ioread32(pdata->vaddr_gpio_mux_quin_ext_clk_ctl);

val = 0x00000001;

iowrite32(val, pdata->vaddr_gpio_mux_quin_ext_clk_ctl);

}

pr_err("msm8952>>>%s: iowrite32 vaddr_gpio_mux_quin_ext_clk_ctln", __func__);

#else

if (pdata->vaddr_gpio_mux_quin_ctl) {

val = ioread32(pdata->vaddr_gpio_mux_quin_ctl);

val = val | 0x00000001;

iowrite32(val, pdata->vaddr_gpio_mux_quin_ctl);

} else {

return -EINVAL;

}

#endif

pr_err("honeywell_msm8952>>>%s: ---001n", __func__);

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = msm_quin_i2s_sclk_ctl(substream, true);

#else

ret = msm_mi2s_sclk_ctl(substream, true);

#endif

if (ret < 0) {

pr_err("honeywell_msm8952>>>%s: failed to enable sclkn", __func__);

return ret;

}

pr_err("honeywell_msm8952>>>%s: ---002n", __func__);

ret = msm_gpioset_activate(CLIENT_WCD_INT, "quin_i2s");

if (ret < 0) {

pr_err("honeywell_msm8952>>>%s: failed to enable codec gpiosn", __func__);

goto err;

}

pr_err("honeywell_msm8952>>>%s: ---003n", __func__);

if (atomic_inc_return(&quin_mi2s_clk_ref) == 1) {

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = snd_soc_dai_set_fmt(cpu_dai, SND_SOC_DAIFMT_CBM_CFM);

#else

ret = snd_soc_dai_set_fmt(cpu_dai, SND_SOC_DAIFMT_CBS_CFS);

#endif

if (ret < 0)

pr_err("honeywell_msm8952>>>%s: set fmt cpu dai failedn", __func__);

}

pr_err("honeywell_msm8952>>>%s: ---004n", __func__);

return ret;

err:

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = msm_quin_i2s_sclk_ctl(substream, false);

#else

ret = msm_mi2s_sclk_ctl(substream, false);

#endif

if (ret < 0)

pr_err("failed to disable sclkn");

return ret;

}

static void msm_quin_mi2s_snd_shutdown(struct snd_pcm_substream *substream)

{

int ret;

pr_err("honeywell_msm8952>>>%s: substream = %s stream = %dn", __func__, substream->name, substream->stream);

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = msm_quin_i2s_sclk_ctl(substream, false);

#else

ret = msm_mi2s_sclk_ctl(substream, false);

#endif

if (ret < 0)

pr_err("honeywell_msm8952>>>%s: clock disable failedn", __func__);

if (atomic_read(&quin_mi2s_clk_ref) > 0)

atomic_dec(&quin_mi2s_clk_ref);

ret = msm_gpioset_suspend(CLIENT_WCD_INT, "quin_i2s");

if (ret < 0) {

pr_err("honeywell_msm8952>>>%s: gpio set cannot be de-activated %sd", __func__, "quin_i2s");

return;

}

}3. Конфигурация часов

(1) Кто дает часы?

Часы в конфигурации часов обеспечиваются MSM8953 или сторонним чипом кодека, который обеспечивается внешним кристаллом, который напрямую связан с основным подчиненным режимом I2S.

Когда I2S является основным режимом, часы имеют внутренний хрустальный генератор MSM8953; наоборот, он предоставляется третьим сторонним кодеком.

Код, настроенный здесь, также установлен в функции MSM_QUIN_MI2S_SND_STARTUP.

Соответствующий сегмент кода индивидуально перехвачен:

#ifdef QUIN_MI2S_USE_SLAVE_MODE

ret = snd_soc_dai_set_fmt(cpu_dai, SND_SOC_DAIFMT_CBM_CFM);

#else

ret = snd_soc_dai_set_fmt(cpu_dai, SND_SOC_DAIFMT_CBS_CFS);

#endif(2) Как так часто частота настройки?

Здесь MSM_MI2S_SCLK_CTL записывает функцию MSM_QUIN_I2S_SCLK_CTL для конфигурации часов рабочего режима.

//added by kuangjincheng @20180521 QUIN_MI2S_SLAVE_MODE config

#ifdef QUIN_MI2S_USE_SLAVE_MODE

static struct afe_clk_set quin_i2s_rx_clk = {

AFE_API_VERSION_I2S_CONFIG,

Q6AFE_LPASS_CLK_ID_QUI_MI2S_EBIT,

Q6AFE_LPASS_OSR_CLK_1_P536_MHZ,

Q6AFE_LPASS_CLK_ATTRIBUTE_COUPLE_NO,

Q6AFE_LPASS_CLK_ROOT_DEFAULT,

0,

};

static struct afe_clk_set quin_i2s_tx_clk = {

AFE_API_VERSION_I2S_CONFIG,

Q6AFE_LPASS_CLK_ID_QUI_MI2S_EBIT,

Q6AFE_LPASS_OSR_CLK_3_P072_MHZ,

Q6AFE_LPASS_CLK_ATTRIBUTE_COUPLE_NO,

Q6AFE_LPASS_CLK_ROOT_DEFAULT,

0,

};

#endif

//added by kuangjincheng @20180521 QUIN_MI2S_SLAVE_MODE config

#ifdef QUIN_MI2S_USE_SLAVE_MODE

static int msm_quin_i2s_sclk_ctl(struct snd_pcm_substream *substream, bool enable)

{

int ret = 0;

struct snd_soc_pcm_runtime *rtd = substream->private_data;

int port_id = 0;

pr_err("msm8952>>>%s: entern", __func__);

port_id = msm8952_get_port_id(rtd->dai_link->be_id);

if (port_id < 0) {

pr_err("msm8952>>>%s: Invalid port_idn", __func__);

return -EINVAL;

}

if (enable) {

if (substream->stream == SNDRV_PCM_STREAM_PLAYBACK) {

quin_i2s_rx_clk.enable = enable;

quin_i2s_rx_clk.clk_id = msm8952_get_clk_id(port_id);

quin_i2s_rx_clk.clk_freq_in_hz = get_mi2s_rx_clk_val(port_id);

ret = afe_set_lpass_clock_v2(port_id, &quin_i2s_rx_clk);

} else if (substream->stream == SNDRV_PCM_STREAM_CAPTURE) {

quin_i2s_tx_clk.enable = enable;

quin_i2s_tx_clk.clk_id = msm8952_get_clk_id(port_id);

quin_i2s_tx_clk.clk_freq_in_hz = Q6AFE_LPASS_OSR_CLK_1_P536_MHZ;

ret = afe_set_lpass_clock_v2(port_id, &quin_i2s_tx_clk);

} else {

pr_err("msm8952>>>%s: Not valid substream.n", __func__);

}

if (ret < 0)

pr_err("msm8952>>>%s: enable: %d, afe_set_lpass_clock_v2 failedn", __func__, enable);

} else {

if (substream->stream == SNDRV_PCM_STREAM_PLAYBACK) {

quin_i2s_rx_clk.enable = enable;

quin_i2s_rx_clk.clk_id = msm8952_get_clk_id(port_id);

ret = afe_set_lpass_clock_v2(port_id, &quin_i2s_rx_clk);

} else if (substream->stream == SNDRV_PCM_STREAM_CAPTURE) {

quin_i2s_tx_clk.enable = enable;

quin_i2s_tx_clk.clk_id = msm8952_get_clk_id(port_id);

ret = afe_set_lpass_clock_v2(port_id, &quin_i2s_tx_clk);

} else {

pr_err("msm8952>>>%s: Not valid substream.n", __func__);

}

if (ret < 0)

pr_err("msm8952>>>%s: enable: %d, afe_set_lpass_clock_v2 failedn", __func__, enable);

}

return ret;

}

#endif4. Сводка и расширение

Приведенный выше код модифицирован для завершения шины I2S из конфигурации режима, а основной субклюк-микрофон можно вырезать на макро определение Quin_MI2S_USE_SLAVE_MODE.

Расширенный:

kernel/msm-3.18/include/uapi/sound/asound.h

kernel/msm-3.18/include/sound/apr_audio-v2.h

Формат PCM можно установить:

SNDRV_PCM_FORMAT_S16_LE

SNDRV_PCM_FORMAT_S24_LE

SNDRV_PCM_FORMAT_S24_3LE

Битовые часы могут быть выбраны для:

/* Supported OSR clock values */

#define Q6AFE_LPASS_OSR_CLK_12_P288_MHZ 0xBB8000

#define Q6AFE_LPASS_OSR_CLK_9_P600_MHZ 0x927C00

#define Q6AFE_LPASS_OSR_CLK_8_P192_MHZ 0x7D0000

#define Q6AFE_LPASS_OSR_CLK_6_P144_MHZ 0x5DC000

#define Q6AFE_LPASS_OSR_CLK_4_P096_MHZ 0x3E8000

#define Q6AFE_LPASS_OSR_CLK_3_P072_MHZ 0x2EE000

#define Q6AFE_LPASS_OSR_CLK_2_P048_MHZ 0x1F4000

#define Q6AFE_LPASS_OSR_CLK_1_P536_MHZ 0x177000

#define Q6AFE_LPASS_OSR_CLK_1_P024_MHZ 0xFA000

#define Q6AFE_LPASS_OSR_CLK_768_kHZ 0xBB800

#define Q6AFE_LPASS_OSR_CLK_512_kHZ 0x7D000

#define Q6AFE_LPASS_OSR_CLK_DISABLE 0x0

/* Supported Bit clock values */

#define Q6AFE_LPASS_IBIT_CLK_12_P288_MHZ 0xBB8000

#define Q6AFE_LPASS_IBIT_CLK_11_P2896_MHZ 0xAC4400

#define Q6AFE_LPASS_IBIT_CLK_8_P192_MHZ 0x7D0000

#define Q6AFE_LPASS_IBIT_CLK_6_P144_MHZ 0x5DC000

#define Q6AFE_LPASS_IBIT_CLK_4_P096_MHZ 0x3E8000

#define Q6AFE_LPASS_IBIT_CLK_3_P072_MHZ 0x2EE000

#define Q6AFE_LPASS_IBIT_CLK_2_P8224_MHZ 0x2b1100

#define Q6AFE_LPASS_IBIT_CLK_2_P048_MHZ 0x1F4000

#define Q6AFE_LPASS_IBIT_CLK_1_P536_MHZ 0x177000

#define Q6AFE_LPASS_IBIT_CLK_1_P4112_MHZ 0x158880

#define Q6AFE_LPASS_IBIT_CLK_1_P024_MHZ 0xFA000

#define Q6AFE_LPASS_IBIT_CLK_768_KHZ 0xBB800

#define Q6AFE_LPASS_IBIT_CLK_512_KHZ 0x7D000

#define Q6AFE_LPASS_IBIT_CLK_256_KHZ 0x3E800

#define Q6AFE_LPASS_IBIT_CLK_DISABLE 0x0Глубина местоположения может быть выбрана: 16, 24

Скорость образца может быть выбрана для:

#define BTSCO_RATE_8KHZ 8000

#define BTSCO_RATE_16KHZ 16000

#define SAMPLING_RATE_48KHZ 48000

#define SAMPLING_RATE_96KHZ 96000

#define SAMPLING_RATE_192KHZ 192000

Эта часть этого раздела находится в документах Qualcomm следующим образом:

CARMEDIA NH-M1206-128-10 (Android 10, MSM 8953PX6 6×2.0 Ghz, 6Gb Ram, <br>128Gb ROM, BT4.0, 1920*1080) Головное устройство на Android 10 для Mercedes GLE <br>/ GLS 2016-2018 NTG 5.0/5.1

CARMEDIA

NH-M1206-128-11 (Android 11, MSM 8953PX6 6×2.0 Ghz, 6Gb Ram, 128Gb ROM, BT4.0, 1920*1080) Головное устройство на

Android 11 для Mercedes

GLE / GLS 2016-2018 NTG 5.0/5.1

Разработка

2022

года от

CARMEDIA

линейка головных устройств

серии

HN Tesla-Style

со встроенным

звуковым процессором

с

TDA 7850,

центральным процессором

MSM

8953PX6

6×2,0 Ghz (6

турбо-ядер), 6Гб оперативной

и128Гб встроенной памяти! Штатное

головное устройство для

Mercedes GLE / GLS 2016-2018 NTG 5.0/5.1 на

Android 11 CARMEDIA

NH-M1206-128-11

со стабильным

шести-ядерным процессором M1206, точной навигацией (GPS,

Глонасс), ярким сенсорным экраном

AHD 1080TVL

и громкой связью идеально подходит для

замены магнитолы на вашем авто! Стиль

Tesla

уникальный и красивый!

В составе графической подсистемы задействован контроллер Mali

T860 MP4 (процессор

способен справляться с декодированием видеоматериалов 1080p

H.265/H.264/VC-1/MPEG/VP8).

Главные преимущества CARMEDIA серии

HN-xxxx-M1206-64-10 Tesla-Style:

-

Встроенный звуковой

процессор TDA 7850 для качественного звука!

Цифровой сенсорный экран c матрицей 1080tvl для Tesla-Style

(морозостойкий)!

Втроенный

4G/LTE модем!-

MSM

8953PX6 6×2.0 Ghz + надежные

комплектующие! -

6Gb

оперативной памяти и 128Gb втроенной! -

Внутренний микрофон полностью

поддерживает голосовой поиск и управление андроид! -

Подддержка

CarPlay! Наличие HDMI

порта! -

NXP 6686 FM цифровой Радио модуль высокой

чувствительности! -

Управление климат-контролем и другими функциями с экрана! -

Сверхточная GPS+Glonass навигация!

Официальный

магазин

CARMEDIA.RU

предлагает только высококачественные комплектующие и самые

последние прошивки, что обеспечивает стабильность и долгую работу головного

устройства!

Описание — CARMEDIA NH-M1206-128-11

Головное устройство на Android 11 для

Mercedes GLE / GLS 2016-2018 NTG

5.0/5.1

- Архитектура процессора

MSM 8953PX6 6x2.0 Ghz - Оперативная память

6 Гб, Встроенная память 128 Гб -

OS

Android 11 - Экран AHD

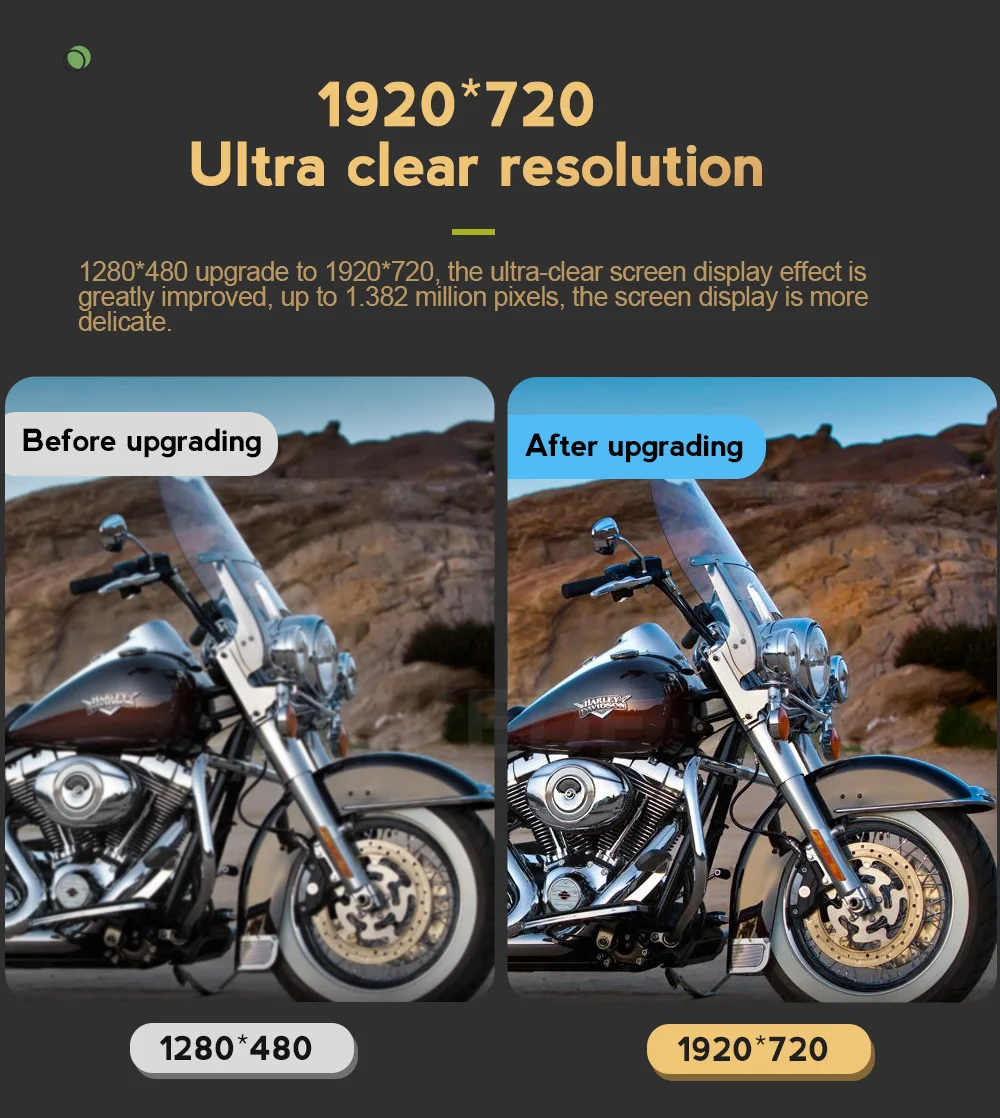

12,3«,

1920*720 - Поддержка разделения экрана!

- Поддержка

CarPlay - Поддержка карт памяти

Поддержка SD карт (на

некоторых моделях), USB flash и HDD до 1 Террабайта

- Wi-Fi (802.11 b/g/n)

150 Mbit встроенный модуль

Встроенный 4G/LTE!

Возможность по WiFi принимать интернет с вашего смартфона (нужно включить на

нем точку доступа WiFi)- Bluetooth встроенный

4.0 - DVD привод

—

отсутствует - Встроенный GPS и

Glonass — UBlox (сверхточный прием)

Радио модуль HD Radio NXP 6686

(используется в аудиосистеме Mercedes и BMW) уверенный приём даже при самом

слабом сигнале- CAN шина

— в комплекте (в некоторых

моделях втроенная) - Поддержка кнопок на

руле - 1*USB OTG, 1*USB HOST (поддержка

HDD дисков, USB drive, Keyboard, Mouse, Вебкамера, Wi-Fi роутеров, зарядка

мобильных и др.), 2 порта (в некоторых устройствах 3 порта) - TV

цифровое —

Лайм.ТВ - Рабочее напряжение

10.8V ~16V - Соотношение сигнал/шум

усилителя 85 dB - Аудио входы 1 линейный

- Аудио выходы

5.1 линейные - Видео входы 1

композитный - Видео выходы 2-х

композитный, HDMI - Выходная мощность

MOSFET TDA7850 4х55Вт,

поддержка четырех-омной и двух-омной(премиум) акустики - Диапазон рабочих

температур -20~+70

Поддержка

IPop, Iphone, смартфоны на OS Android- Поддержка

датчиков давления в шинах - Поддержка ИК пульта*

(в некоторых моделях не комплектуется)

Поддержка

камеры заднего хода

- Яркость и подсветка

кнопок*

Комплектация —

CARMEDIA NH-M1206-128-11 Головное устройство на

Android 11 для

Mercedes GLE / GLS 2016-2018 NTG

5.0/5.1

- Головное устройство

Tesla Style - Жгут проводов для

подключения к штатным разъемам автомобиля

- Адаптер CAN-шины для

поддержки штатных функций

(для определенных встроенный)

- Жгут «тюльпанов» для

усилителя, сабвуфера, AUX и камеры заднего вида

- Внешний микрофон для

громкой связи - GPS антенна для

навигации

- Гарантийный талон

CARMEDIA (гарантия 2 года)

Официальный интернет-магазин

www.carmedia.ru

Теги: Цена

головное устройство CARMEDIA NH-M1206-128-11

для Mercedes GLE / GLS 2016-2018 NTG 5.0/5.1,

купить

CARMEDIA NH-M1206-128-11, доставка

CARMEDIA NH-M1206-128-11, установка

CARMEDIA NH-M1206-128-11,

характеристики

CARMEDIA NH-M1206-128-11

Mercedes GLE / GLS 2016-2018 NTG 5.0/5.1 CARMEDIA

NH-M1206-128-11

(Android 11, MSM 8953PX6 6×2.0 Ghz, 6Gb Ram, 128Gb ROM, BT4.0, 1920*1080) Штатное головное мультимедийное устройство

*

уточняйте при заказе (некоторые опции могут отсутствовать в начальной

комплектации)

Вчем привет. Ребят помогите! Нужна схема подключения этой магнитоллы. МНЕ ЕЕ КОРЯВО УСТАНОВИЛИ СХЕМУ ПОТЕРЯЛИ. Mmi глючит и не хочет с ней работать.

Приезжала Q7 4l с подобной прибоудой, у неё потребление в спящем от приборки в 300mA, возможно ли такое от этого монитора? он вешвется в одну цепь, не вкурсе?

Надо пробовать методом исключения

Вариант отличный, именно он в первую очередь и пришел в голову мне, подкинуть родной MMI, чем я и займусь. Но если проблема будет и в магнитоле, не могу понять, с чего начать смотреть, учитывая что инструкции по этому китайскому прибору нигде нет

Похоже ни как, 300мА это дежурка возможно. И скорее надо искать провод который её отключает. Или. Коричневую коробочку вскрыть. Смотреть что греется в магнитоле.

Проблема оказалась из за магнитолы, а именно ложила can шину или пробуждала mmi по оптике. Перевешал питание транспондера оптики с 30 клеммы на 15 и это частично помогло, но теперь нельзя воспользоваться mmi без включённого зажигания

Привет

Подскажи пожалуйста — удалось поставить?

Здравствуйте, все поставили, работает

Можно телефон владельца? Я такую же себе купил

Есть ряд вопросов

Не сохранил, обычно мне звонят

У меня не работает автояркость

И нет индикации климата поверх андроида

Все фото

4.5

-

165 г, 8.45 мм -

Android 7.0

-

5.5″

1080 x 1920

-

12.98mp

-

4/3/2Gb RAM

Qualcomm Snapdragon 625 MSM8953

-

4100mAh

Li-polymer

-

Установка официальной прошивки | Fastboot

Описание

Подробная инструкция по установке официальной прошивки на Xiaomi Redmi Note 4X и Xiaomi Redmi Note 4 Qualcomm (Mido) с разблокированным загрузчиком.

-

Драйвера и программы

-

MiPhoneSetup.zip

Скачать

-

MiFlash.zip

Скачать

-

adb-fastboot.zip

Скачать

-

Инструкция по установке

-

1

Сделать резервные копии всех необходимых данных и файлов и сохранить их на компьютер, съёмный носитель или облако.

-

2

Создать в корне диска С: папку с именем «Android».

-

3

Отключить проверку подлинности драйверов.

Windows 7

Во время включения компьютера, после загрузки BIOS, необходимо нажать клавишу F8. В появившимся меню «Дополнительные варианты загрузки» выбрать «Отключение обязательной подписи драйверов». Данный способ может сработать не с первого раза, поэтому следует повторить действие либо открыть командную строку от имени администратора и ввести две команды:

«bcdedit.exe /set loadoptions DDISABLE_INTEGRITY_CHECKS»

«bcdedit.exe /set TESTSIGNING ON»

Windows 8

Нужно нажать сочетание клавиш Win+I, зажать клавишу Shift и выбрать пункт «Выключение» > «Перезагрузка». При включении компьютера выбрать «Диагностика» > «Дополнительные параметры» > «Параметры загрузки» > «Перезагрузить». При загрузке выбрать режим «Отключить обязательную проверку подписи драйверов», нажав клавишу F7.

Windows 10

Необходимо зажать клавишу Shift и выбрать меню «Пуск» > «Выключение» > «Перезагрузка». После загрузки выбрать «Поиск и устранение неисправностей» > «Дополнительные параметры» > «Параметры загрузки» > «Перезагрузить». Затем выбрать пункт «Отключить обязательную проверку подписи драйверов», нажав клавишу F7. -

4

Скачать приложение MiFlash.

Примечание:

Если уже установлена программа Mi PC Suite, данный шаг можно пропустить. -

5

Скачать архив adb-fastboot.zip и распаковать все файлы в папку «Android».

-

6

Скачать архив с прошивкой для Fastboot в формате *.tgz и распаковать все файлы в папку «Android».

-

7

Активировать пункты «Заводская разблокировка», «Отладка по USB» и «Режим Fastboot» на смартфоне.

Сделать это можно в разделе «Для разработчиков». Как его открыть, можно узнать здесь. -

8

Подключить телефон к компьютеру по USB-кабелю.

Рекомендуется использовать оригинальный или кабель хорошего качества, а также порт USB 2.0, расположенный на материнской плате (для ПК). -

9

Открыть командную строку и перейти в созданную папку Android командой «cd c:Android» (команды пишутся без кавычек).

-

10

Убедиться, что компьютер находит устройство по ADB.

Для этого необходимо ввести «adb devices» в командную строку. На появившейся запрос на телефоне о разрешении об отладке по ADB на данном компьютере необходимо нажать «Ok», при этом выбрав пункт «Всегда разрешать с этого компьютера». Если устройство видно, то выведется текст «List of devices attached» и список всех устройств (например,xxxxxxx device). Если же вместо «device» будет написано «offline» либо список окажется пустым, то необходимо обновить ADB, проверить драйвера/шнур, поменять порт USB/компьютер. -

11

Перезагрузить смартфон в режим Fastboot.

Для этого необходимо в командной строке ввести «adb reboot bootloader» либо выключить его, затем включить с зажатой клавишей Уменьшения Громкости. На экране должен отобразиться заяц в шапке-ушанке. -

12

Убедиться, что компьютер находит устройство в режиме Fastboot.

Для этого необходимо ввести команду «fastboot devices». Если в ответ выведется «xxxxxxx fastboot» значит телефон подключён верно. Если же выводится «waiting for device» или же вообще ничего — необходимо проверить состояние USB-подключения либо переустановить драйвера. -

13

В командной строке ввести «flash_all.bat» для установки прошивки с удалением всех пользовательских данных либо «flash_all_except_data_storage.bat» для прошивки с их сохранением.

Начнётся процесс установки прошивки. -

14

Через некоторое время устройство само перезагрузится в систему и будет готово к дальнейшей работе.

Если этого не произошло, необходимо в командной строке ввести «fastboot reboot» либо зажать кнопку Включения примерно на 10 секунд.

-

Список инструкции для Xiaomi Redmi Note 4 MSM8953

-

Переход с глобальной стабильной на прошивку для разработчиков

-

Установка официальной прошивки | XiaoMiTool

-

Установка официальной прошивки | MiFlash

-

Установка кастомной прошивки

-

Установка кастомного рекавери и получение рут-прав

-

Разблокировка загрузчика

Список прошивок для Xiaomi Redmi Note 4 MSM8953

-

Официальная глобальная прошивка для разработчиков | Recovery

-

Официальная китайская прошивка для разработчиков | Recovery

-

Официальная глобальная стабильная прошивка | Recovery

-

Официальная глобальная стабильная прошивка | Fastboot

Регистрация прошла успешно

История изменения цены

MSM8953 4G LTE HD 8 ядер Android 10 0 встроенный CarPlay автомобильный мультимедийный плеер

Двойное преобразование системы, оригинальная система Mercedes Benz NTG и система Android.

Двойное преобразование системы, оригинальная система Mercedes Benz NTG и система Android.

Поддержка всех оригинальных функций NTG, таких как заводское радио, gps-навигация, bluetooth, DVD/CD,USB,SD и т. д., поддержка заводской камеры заднего вида обратного траектории. Камера 360, дверная открывающаяся, совместима с оригианловым джойстиком, сенсорной мышью и управлением рулем, совместима с оригинальной звуковой системой и оптическим волокном, проигрывает аудио без потерь.Новые модели и новый пользовательский интерфейс, больше похоже на оригинальный стиль автомобиля, более стильныйПримечание: При оформлении заказа, пожалуйста, проверьте, что ваш автомобиль NTG 4,0 или 4,5 или 5,0. Если у вас есть какие-либо сомнения, пожалуйста, свяжитесь с нашим персоналом по обслуживанию клиентов.Автомобильный мультимедийный плеер подходит дляДля Benz C-Class W204 2007 до 2010 NTG 4,0

> ПоддержкаВидеорегистраторFuntion> Вы можете смотреть видео на радио, подключив USB. Легко подключить и легко смотреть. Сделайте вас безопаснее в дороге. (дополнительный аксессуар)

> ПоддержкаВидеорегистраторFuntion> Вы можете смотреть видео на радио, подключив USB. Легко подключить и легко смотреть. Сделайте вас безопаснее в дороге. (дополнительный аксессуар)

>ADASФункция, Предупреждение о столкновении, Предупреждение о выезде переднего транспортного средства, делает вас более безопасными на дороге.

>Поддержка задней камеры

**Когда автомобиль находится на заднем ходу, Этот автомобильный DVD автоматически переключается на изображение камеры заднего вида с помощью линии парковки. (дополнительный аксессуар)

>CarPlayЭто более умный, безопасный способ использования вашего iPhone в автомобиле. CarPlay принимает то, что вы хотите сделать с вашим iPhone во время вождения, и кладет их прямо на встроенный дисплей вашего автомобиля. Вы можете получать указания, совершать звонки, отправлять и получать сообщения, а также слушать музыку, таким образом, чтобы вы могли оставаться сосредоточенными на дороге. Просто подключите ваш iPhone и перейдите.

Функция BT:Автомобильная стереосистема оснащена встроенным Bluetooth и функцией телефонной книги. Вы можете синхронизировать телефонную книгу с вашего мобильный телефон на этот блок, а затем сделать мобильный телефон без рук удобным и быстрым. Вы также можете наслаждаться беспроводным воспроизведением музыки с вашего устройства bluetooth.

Поддержка зеркального соединения:Любое содержимое смартфона Android или IOS может отображаться на экране устройства, поэтому вы можете смотреть видео на большом дисплее, для телефона android, вы даже можете достичь Двунаправленного управления с помощью usb-кабеля для доступа к телефонной книге, карте, музыке и многому другому.

Встроенный gps-навигатор** Встроенная GPS/ГЛОНАСС навигация** Встроенная карта, постоянно обновляется** О обновлении карты: если вы хотите обновить карту, пожалуйста, свяжитесь с нами, мы загрузим ее в «Drop box», пожалуйста, не загружайте в других местах, В противном случае это повредит оригинальную карту.** Об обновлении карты:Если вы хотите обновить карту, пожалуйста, свяжитесь с нами, мы загрузим ее в «Drop box», пожалуйста, не загружайте в других местах, в противном случае это повредит оригинальную карту.> Время обновления карты: один раз в год

Встроенный gps-навигатор** Встроенная GPS/ГЛОНАСС навигация** Встроенная карта, постоянно обновляется** О обновлении карты: если вы хотите обновить карту, пожалуйста, свяжитесь с нами, мы загрузим ее в «Drop box», пожалуйста, не загружайте в других местах, В противном случае это повредит оригинальную карту.** Об обновлении карты:Если вы хотите обновить карту, пожалуйста, свяжитесь с нами, мы загрузим ее в «Drop box», пожалуйста, не загружайте в других местах, в противном случае это повредит оригинальную карту.> Время обновления карты: один раз в год

Отзывы покупателей

*о других товарах на сайте

Отзывы о MSM8953 4G LTE HD 8 ядер Android 10 0 встроенный CarPlay автомобильный мультимедийный

Здесь вы можете оставить свой отзыв о данном товаре.